## **CHAPTER 8**

## **ANALOG & DIGITAL ELECTRONICS**

#### **PAGE 420**

#### **ANALOG & DIGITAL ELECTRONICS**

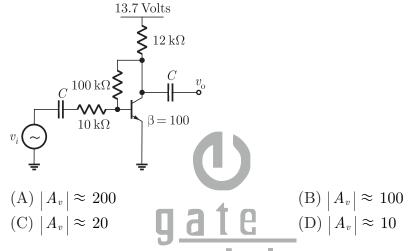

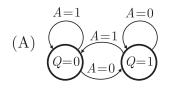

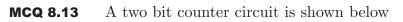

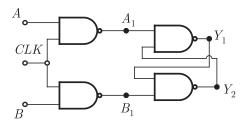

In this circuit, the race around

- (A) does not occur

- (B) occur when CLK = 0

- (C) occur when CLK = 1 and A = B = 1

- (D) occur when CLK = 1 and A = B = 0

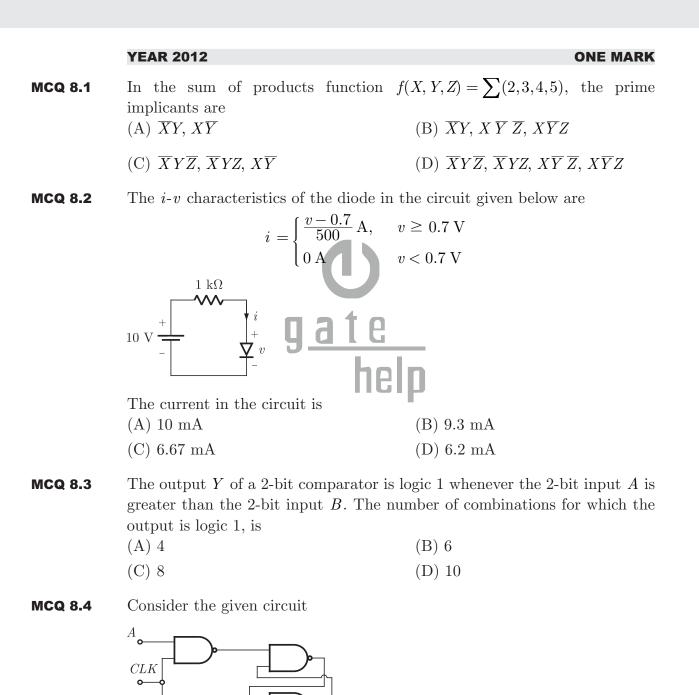

## **YEAR 2012**

**TWO MARKS**

**MCQ 8.6**

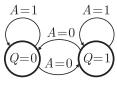

**8.6** The state transition diagram for the logic circuit shown is

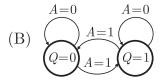

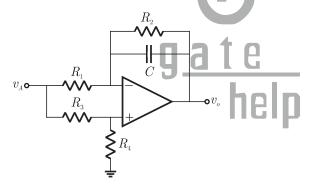

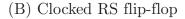

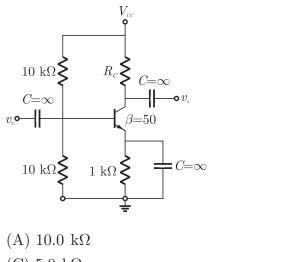

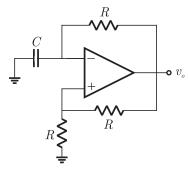

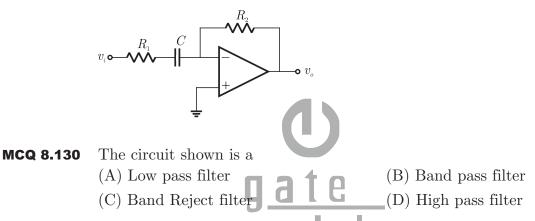

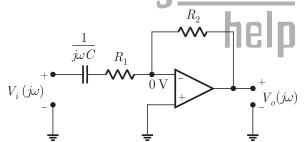

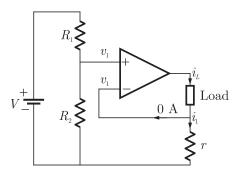

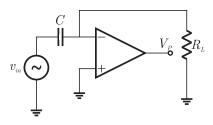

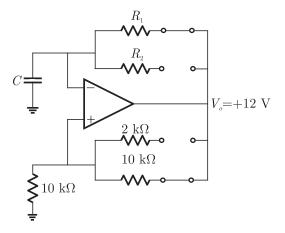

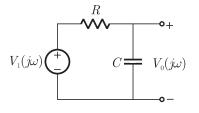

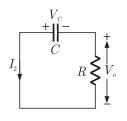

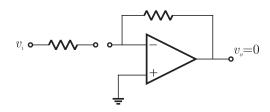

#### The circuit shown is a **MCQ 8.7**

- (A) low pass filter with  $f_{3dB} = \frac{1}{(R_1 + R_2)C}$  rad/s

- (B) high pass filter with  $f_{3dB} = \frac{1}{R_1 C} \text{ rad/s}$

(C) low pass filter with

$$f_{3dB} = \frac{1}{R_1 C} \text{ rad/s}$$

(D) high pass filter with  $f_{3dB} = \frac{1}{(R_1 + R_2) C} \text{ rad/s}$

## **YEAR 2011**

# **ONE MARK**

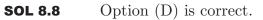

- A low-pass filter with a cut-off frequency of 30 Hz is cascaded with a high **MCQ 8.8** pass filter with a cut-off frequency of 20 Hz. The resultant system of filters will function as help

- (A) an all pass filter

- (B) an all stop filter

- (C) an band stop (band-reject) filter

- (D) a band pass filter

## **MCQ 8.9**

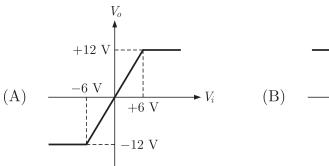

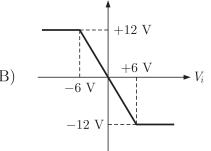

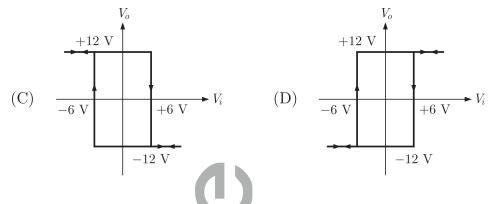

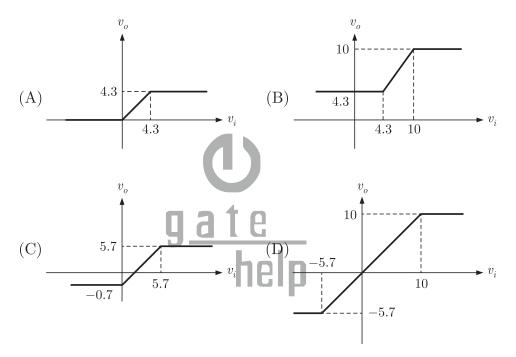

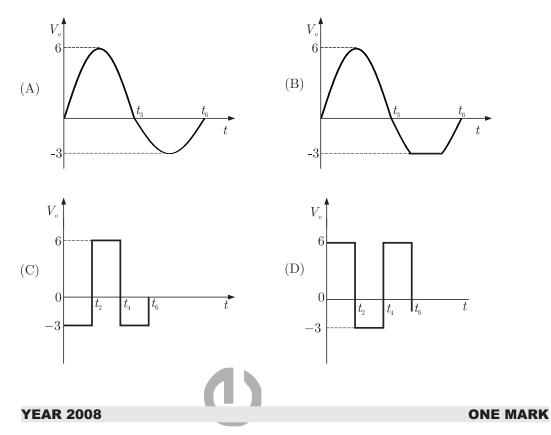

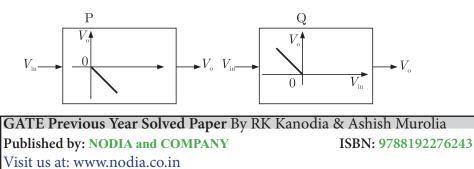

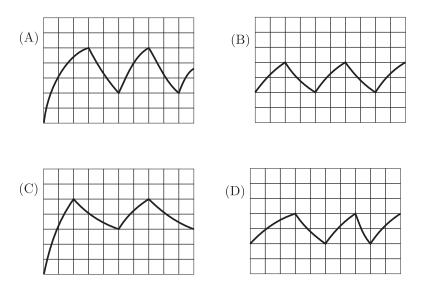

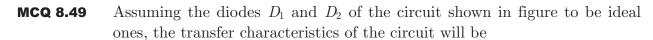

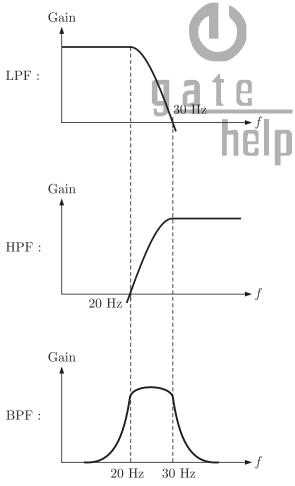

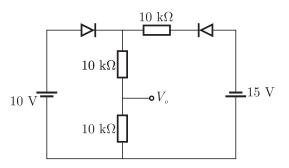

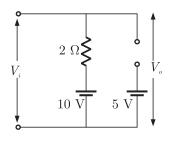

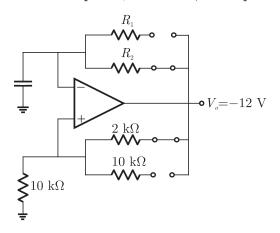

The CORRECT transfer characteristic is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

#### **CHAP 8**

$V_o$

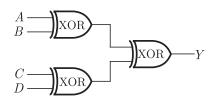

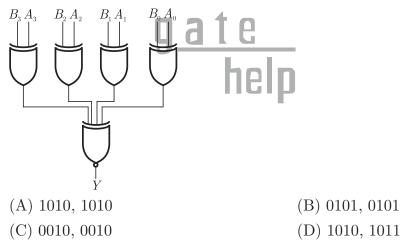

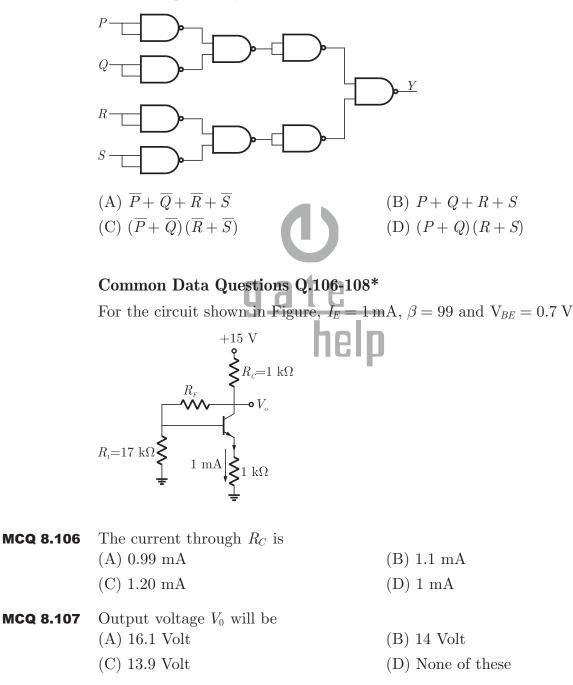

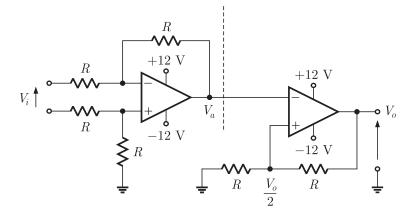

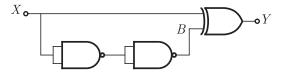

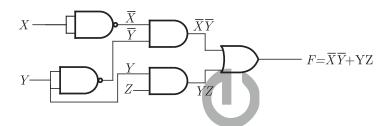

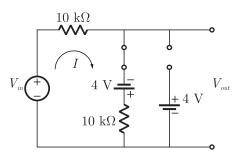

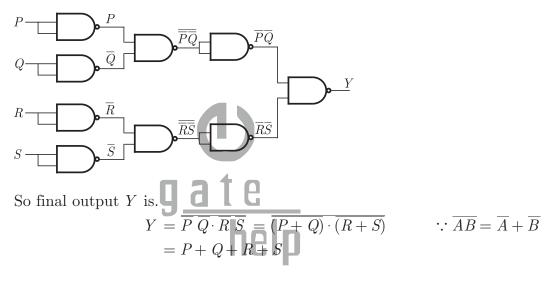

**MCQ 8.10** The output Y of the logic circuit given below is

## YEAR 2011

## **TWO MARKS**

**MCQ 8.11** A portion of the main program to call a subroutine SUB in an 8085 environment is given below.

: LXI D, DISP LP : CALL SUB LP+3 :

It is desired that control be returned to LP+DISP+3 when the RET instruction is executed in the subroutine. The set of instructions that precede the RET instruction in the subroutine are

| CHAP 8 |                              | ANALOG & DIGITAL ELECTRONICS                                                                       | <b>PAGE 423</b> |

|--------|------------------------------|----------------------------------------------------------------------------------------------------|-----------------|

|        | POP D<br>(A) DAD H<br>PUSH D | $(B) \begin{array}{c} POP & H \\ DAD & D \\ INX & H \\ INX & H \\ INX & H \\ PUSH & H \end{array}$ |                 |

|        | POP H<br>(C) DAD D<br>PUSH H | XTHL<br>INX D<br>(D) INX D<br>INX D<br>XTHL                                                        |                 |

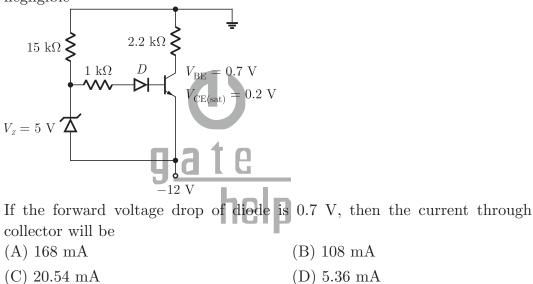

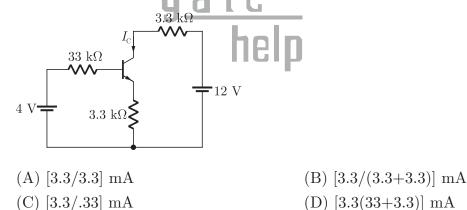

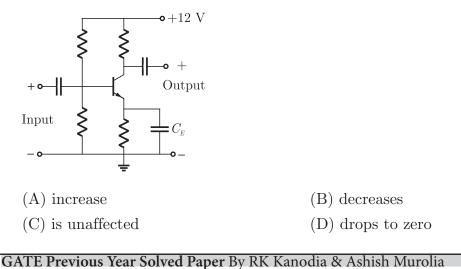

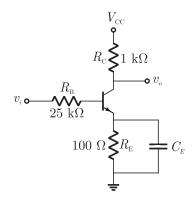

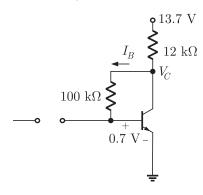

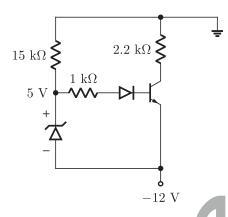

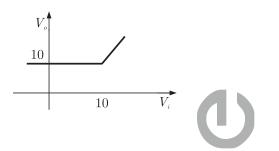

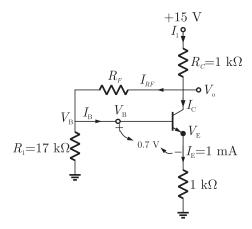

**MCQ 8.12** The transistor used in the circuit shown below has a  $\beta$  of 30 and  $I_{CBO}$  is negligible

It the state  $Q_A Q_B$  of the counter at the clock time  $t_n$  is '10' then the state  $Q_A Q_B$  of the counter at  $t_n + 3$  (after three clock cycles) will be (A) 00 (B) 01

(D) 11

#### **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

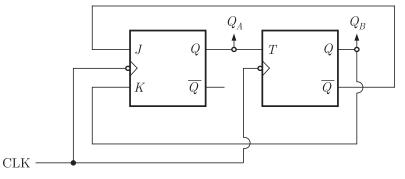

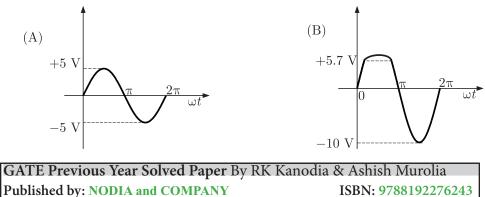

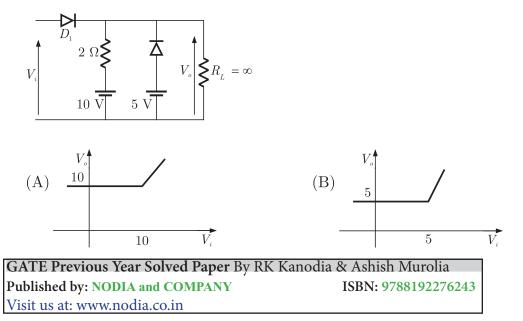

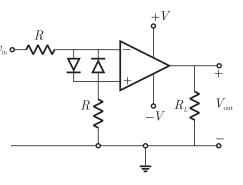

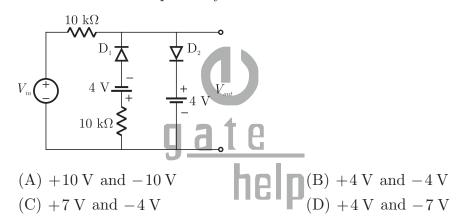

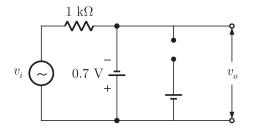

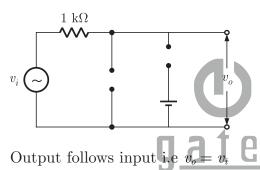

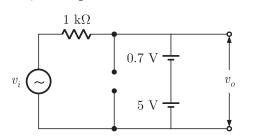

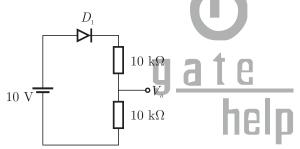

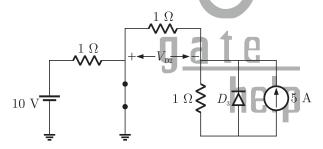

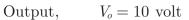

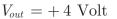

**MCQ 8.14** A clipper circuit is shown below.

Assuming forward voltage drops of the diodes to be 0.7 V, the input-output transfer characteristics of the circuit is

## **YEAR 2010**

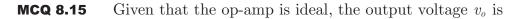

**ONE MARK**

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## **PAGE 424**

| ANALOG & DIGITAL ELECTRONICS |

|------------------------------|

**PAGE 425**

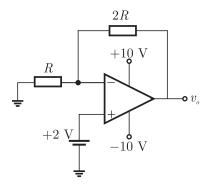

| (A) 4 V   | (B) 6 V     |

|-----------|-------------|

| (C) 7.5 V | (D) 12.12 V |

## **YEAR 2010**

**TWO MARKS**

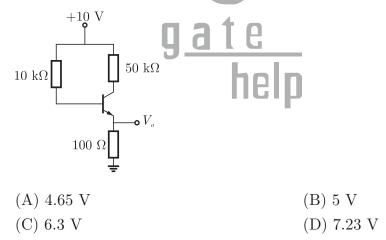

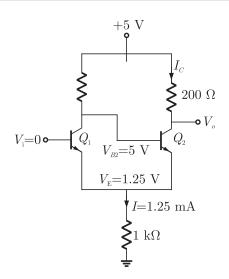

**MCQ 8.17** The transistor circuit shown uses a silicon transistor with  $V_{BE} = 0.7$ ,  $I_C \approx I_E$  and a dc current gain of 100. The value of  $V_0$  is

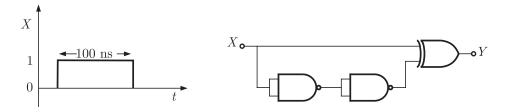

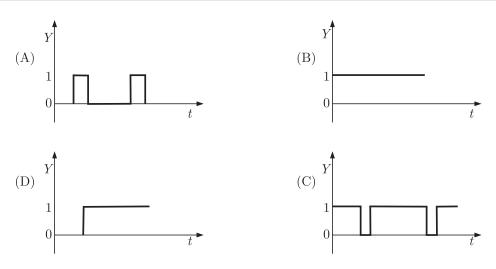

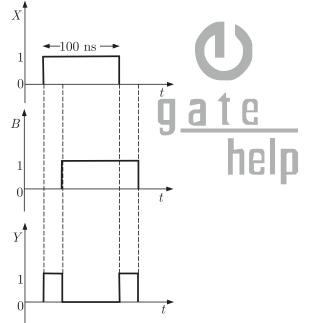

**MCQ 8.18** The TTL circuit shown in the figure is fed with the waveform X (also shown). All gates have equal propagation delay of 10 ns. The output Y of the circuit is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

## CHAP 8

#### **PAGE 426**

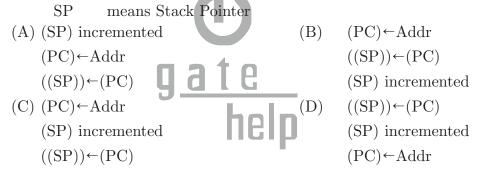

**MCQ 8.19** When a "CALL Addr" instruction is executed, the CPU carries out the following sequential operations internally :

Note: (R) means content of register R

- ((R)) means content of memory location pointed to by R.

- PC means Program Counter

## Statement For Linked Answer Questions: 6 & 7

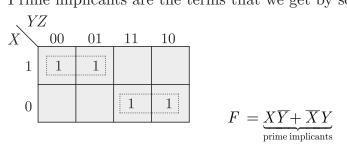

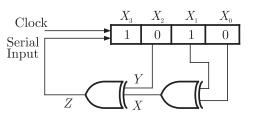

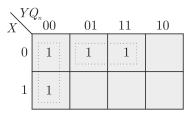

The following Karnaugh map represents a function F.

| F<br>X | $Z_{00}$ | 01 | 11 | 10 |

|--------|----------|----|----|----|

| 0      | 1        | 1  | 1  | 0  |

| 1      | 0        | 0  | 1  | 0  |

| MCQ 8.20 | A minimized form of the function $F$ is              |                                                      |

|----------|------------------------------------------------------|------------------------------------------------------|

|          | (A) $F = \overline{X} Y + YZ$                        | (B) $F = \overline{X} \overline{Y} + YZ$             |

|          | (C) $F = \overline{X} \overline{Y} + Y \overline{Z}$ | (D) $F = \overline{X} \overline{Y} + \overline{Y} Z$ |

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |  |  |

|----------------------------------------------------------------|---------------------|--|--|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |  |  |

| Visit us at: www.nodia.co.in                                   |                     |  |  |  |

#### ANALOG & DIGITAL ELECTRONICS

**PAGE 427**

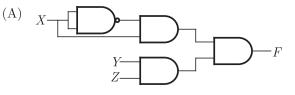

**MCQ 8.21** Which of the following circuits is a realization of the above function F?

## **YEAR 2009**

## **ONE MARK**

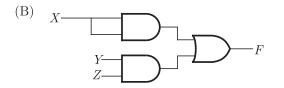

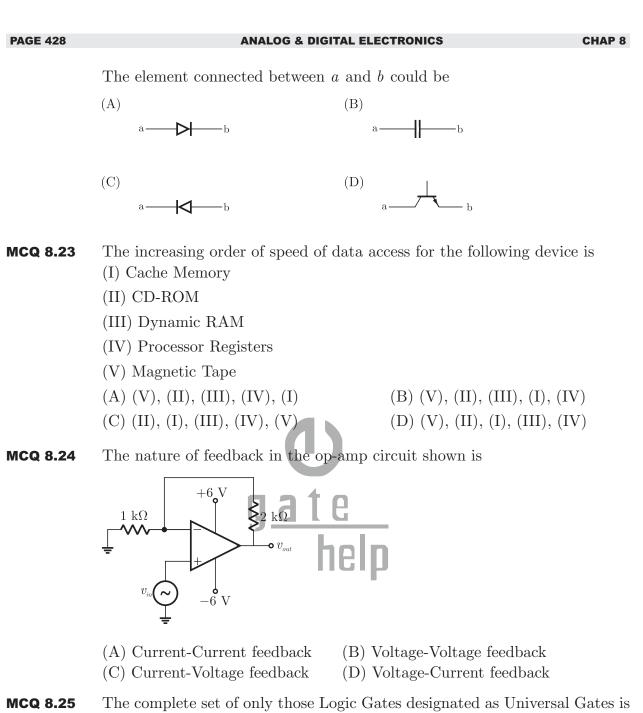

**MCQ 8.22** The following circuit has a source voltage  $V_s$  as shown in the graph. The current through the circuit is also shown.

## CHAP 8

- (A) NOT, OR and AND Gates

- (B) XNOR, NOR and NAND Gates

- (C) NOR and NAND Gates

- (D) XOR, NOR and NAND Gates

## **YEAR 2009**

## TWO MARKS

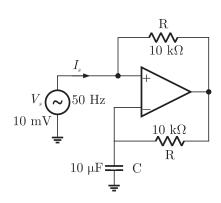

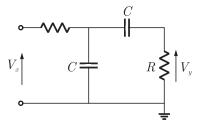

**MCQ 8.26** The following circuit has  $R = 10 \text{ k}\Omega$ ,  $C = 10 \mu\text{F}$ . The input voltage is a sinusoidal at 50 Hz with an rms value of 10 V. Under ideal conditions, the current  $I_{\text{s}}$  from the source is

- (A)  $10\pi$  mA leading by  $90^{\circ}$ (B)  $20\pi$  mA leading by  $90^{\circ}$ (C)  $10\pi$  mA leading by  $90^{\circ}$ (D)  $10\pi$  mA lagging by  $90^{\circ}$

- **MCQ 8.27** Transformer and emitter follower can both be used for impedance matching at the output of an audio amplifier. The basic relationship between the input power  $P_{in}$  and output power  $P_{out}$  in both the cases is (A)  $P_{in} = P_{out}$  for both transformer and emitter follower

- (B)  $P_{in} > P_{out}$  for both transformer and emitter follower

- (C)  $P_{in} < P_{out}$  for transformer and  $P_{in} = P_{out}$  for emitter follower

- (D)  $P_{in} = P_{out}$  for transformer and  $P_{in} < P_{out}$  for emitter follower

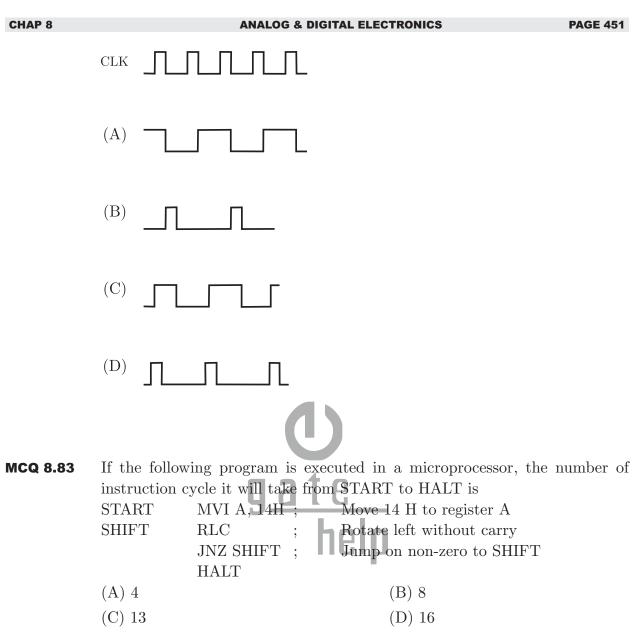

- **MCQ 8.28** In an 8085 microprocessor, the contents of the Accumulator, after the following instructions are executed will become

|          | XRA | А       | hein     |

|----------|-----|---------|----------|

|          | MVI | B, F0 H | help     |

|          | SUB | В       |          |

| (A) 01 H |     |         | (B) 0F H |

| (C) F0 H |     |         | (D) 10 H |

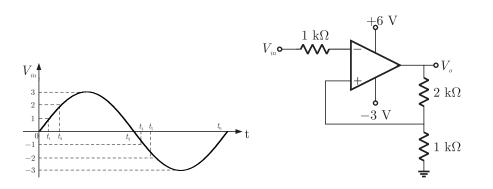

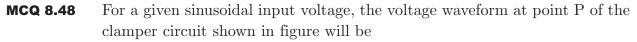

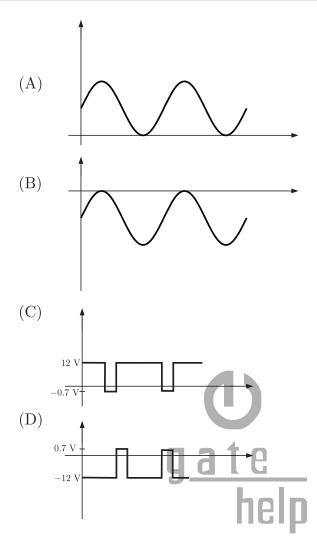

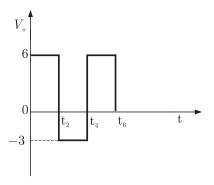

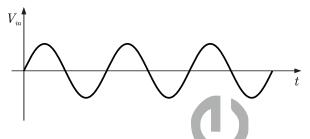

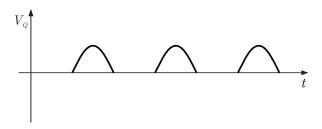

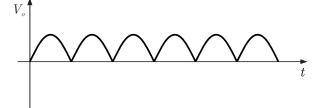

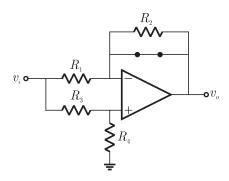

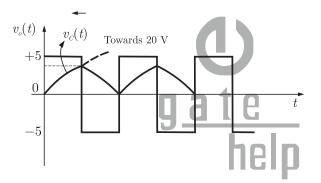

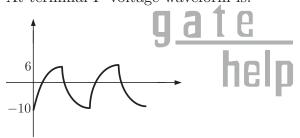

**MCQ 8.29** An ideal op-amp circuit and its input wave form as shown in the figures. The output waveform of this circuit will be

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

**PAGE 430**

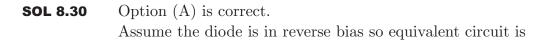

- The equivalent circuits of a diode, during forward biased and reverse biased **MCQ 8.30** conditions, are shown in the figure.

- (I)

5 V

If such a diode is used in clipper circuit of figure given above, the output voltage  $V_0$  of the circuit will be

Visit us at: www.nodia.co.in

ISBN: 9788192276243

## **YEAR 2008**

**TWO MARKS**

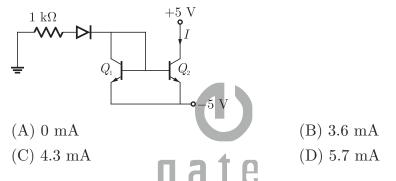

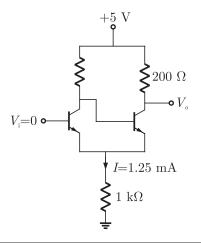

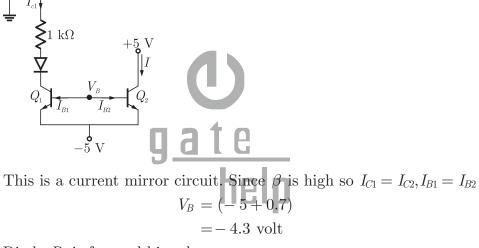

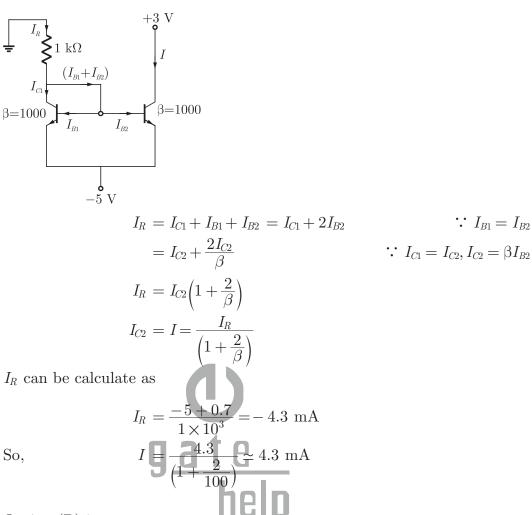

**MCQ 8.31** Two perfectly matched silicon transistor are connected as shown in the figure assuming the  $\beta$  of the transistors to be very high and the forward voltage drop in diodes to be 0.7 V, the value of current I is

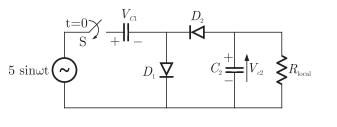

**MCQ 8.32** In the voltage doubler circuit shown in the figure, the switch 'S' is closed at t = 0. Assuming diodes  $D_1$  and  $D_2$  to be ideal, load resistance to be infinite and initial capacitor voltages to be zero. The steady state voltage across capacitor  $C_1$  and  $C_2$  will be

## **PAGE 432**

#### **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

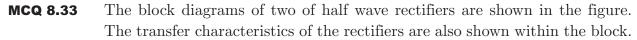

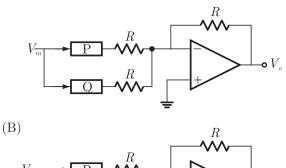

It is desired to make full wave rectifier using above two half-wave rectifiers. The resultants circuit will be

$(\mathbf{A})$

(C)

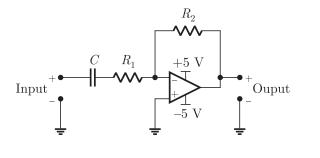

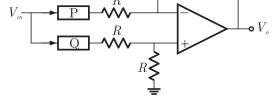

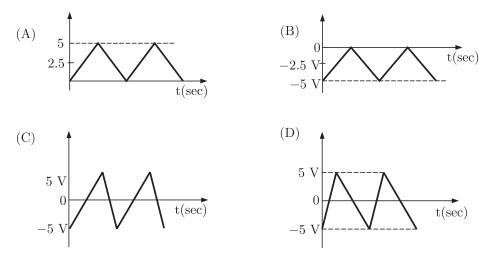

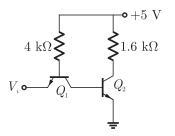

**MCQ 8.34** A waveform generator circuit using OPAMPs is shown in the figure. It produces a triangular wave at point 'P' with a peak to peak voltage of 5 V for  $V_i = 0$  V.

CHAP 8

**PAGE 433**

If the voltage  $V_i$  is made +2.5 V, the voltage waveform at point 'P' will become

## Statement for Linked Answer Questions 21 and 22.

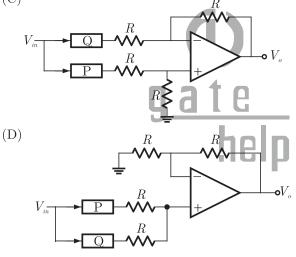

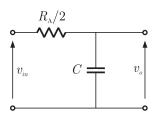

A general filter circuit is shown in the figure :

| MCQ 8.35 | If $R_1 = R_2 = R_A$ and $R_3 = R_4 = R_B$ , the | ne circuit acts as a |

|----------|--------------------------------------------------|----------------------|

|          | (A) all pass filter                              | (B) band pass filter |

|          | (C) high pass filter                             | (D) low pass filter  |

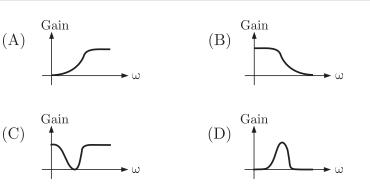

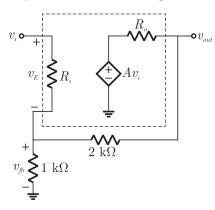

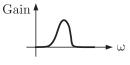

The output of the filter in Q.21 is given to the circuit in figure : **MCQ 8.36** The gain v/s frequency characteristic of the output  $(v_o)$  will be

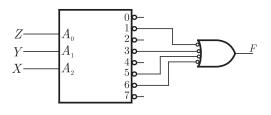

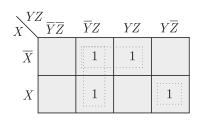

**MCQ 8.37** A 3-line to 8-line decoder, with active low outputs, is used to implement a 3-variable Boolean function as shown in the figure

The simplified form of Boolean function F(A, B, C) implemented in 'Product of Sum' form will be

(A)

$$(X + Z)(\overline{X} + \overline{Y} + \overline{Z})(Y + Z)$$

(B)  $(\overline{X} + \overline{Z})(X + Y + Z)(\overline{Y} + \overline{Z})$

(C)  $(\overline{X} + \overline{Y} + Z)(\overline{X} + Y + Z)(X + \overline{Y} + Z)(X + Y + \overline{Z})$

(D)  $(\overline{X} + \overline{Y} + Z)(\overline{X} + Y + \overline{Z})(X + \overline{Y} + Z)(X + \overline{Y} + \overline{Z})$

**MCQ 8.38** The content of some of the memory location in an 8085 accumulator based system are given below

| Address | Content |

|---------|---------|

| •••     | •••     |

| 26FE    | 00      |

| 26FF    | 01      |

| 2700    | 02      |

| 2701    | 03      |

| 2702    | 04      |

| • • •   | •••     |

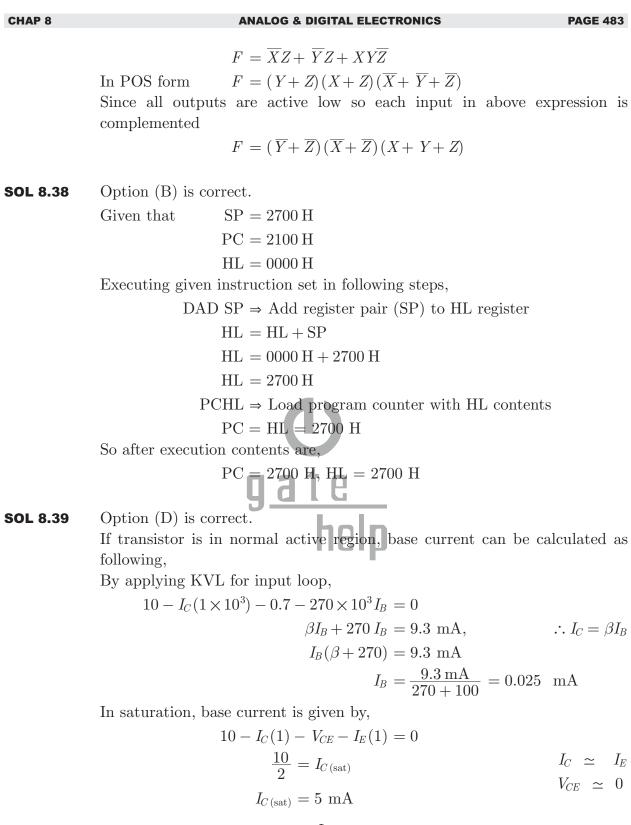

The content of stack (SP), program counter (PC) and (H,L) are 2700 H, 2100 H and 0000 H respectively. When the following sequence of instruction are executed.

2100 H: DAD SP

2101 H: PCHL

the content of (SP) and (PC) at the end of execution will be

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |

|----------------------------------------------------------------|--|--|

| Published by: NODIA and COMPANY ISBN: 9788192276243            |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |

| CHAP 8   | ANALOG & DIGITAL ELECTRONICS                                     |                                                        |                 |

|----------|------------------------------------------------------------------|--------------------------------------------------------|-----------------|

|          | (A) $PC = 2102 H, SP = 2700 H$<br>(C) $PC = 2800 H, SP = 26FE H$ | (B) $PC = 2700 H, SP = 2$<br>(D) $PC = 2A02 H, SP = 2$ |                 |

|          | YEAR 2007                                                        | O                                                      | IE MARK         |

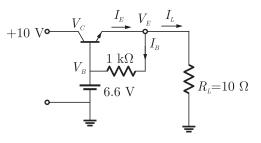

| MCQ 8.39 | The common emitter forward current g                             | ain of the transistor shown is                         | $\beta_F = 100$ |

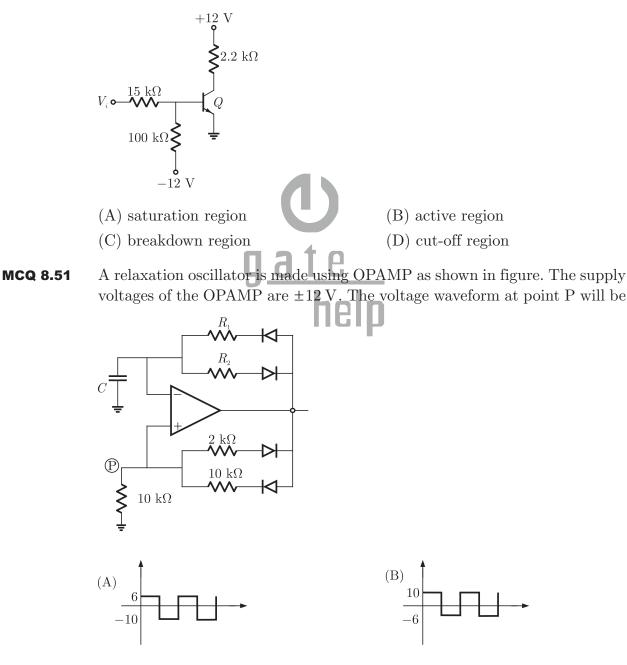

The transistor is operating in

- (A) Saturation region

- (C) Reverse active region

- (B) Cutoff region

- (D) Forward active region

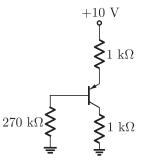

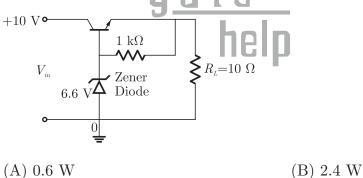

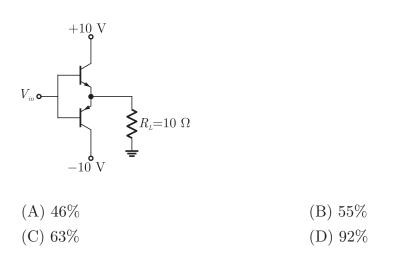

- **MCQ 8.40** The three-terminal linear voltage regulator is connected to a 10  $\Omega$  load resistor as shown in the figure. If  $V_{in}$  is 10 V, what is the power dissipated in the transistor ?

- (C) 4.2 W (D) 5.4 W

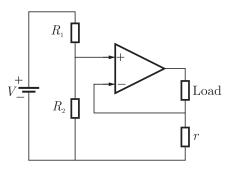

- MCQ 8.41

The circuit shown in the figure is

- (A) a voltage source with voltage  $\frac{rV}{R_1 \parallel R_2}$ (B) a voltage source with voltage  $\frac{r \parallel R_2}{R_1} V$ (C) a current source with current  $\left(\frac{r \parallel R_2}{R_1 + R_2}\right) \frac{V}{r}$ (D) a current source with current  $\left(\frac{R_2}{R_1 + R_2}\right) \frac{V}{r}$

- **MCQ 8.42** A, B, C and D are input, and Y is the output bit in the XOR gate circuit of the figure below. Which of the following statements about the sum S of A, B, C, D and Y is correct?

**YEAR 2007**

(A) S is always with zero or odd

(B) S is always either zero or even

- (C) S = 1 only if the sum of A, B, C and D is even

- (D) S = 1 only if the sum of A, B, C and D is odd

## **TWO MARKS**

**MCQ 8.43** The input signal  $V_{in}$  shown in the figure is a 1 kHz square wave voltage that alternates between +7 V and -7 V with a 50% duty cycle. Both transistor have the same current gain which is large. The circuit delivers power to the load resistor  $R_L$ . What is the efficiency of this circuit for the given input ? choose the closest answer.

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

CHAP 8

#### ANALOG & DIGITAL ELECTRONICS

#### **PAGE 437**

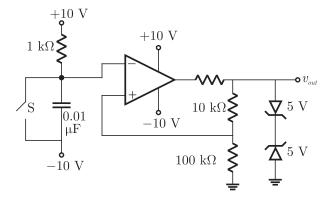

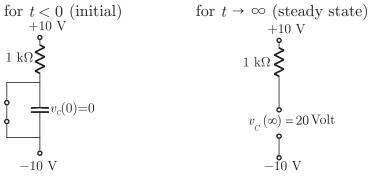

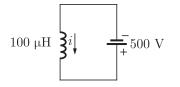

**MCQ 8.44** The switch S in the circuit of the figure is initially closed, it is opened at time t = 0. You may neglect the zener diode forward voltage drops. What is the behavior of  $v_{out}$  for t > 0?

- (A) It makes a transition from -5 V to +5 V at  $t = 12.98 \,\mu s$

- (B) It makes a transition from -5 V to +5 V at  $t = 2.57 \,\mu s$

- (C) It makes a transition from +5 V to -5 V at  $t = 12.98 \,\mu s$

- (D) It makes a transition from +5 V to -5 V at  $t = 2.57 \ \mu s$

- MCQ 8.45

The Octal equivalent of HEX and number AB.CD is

(A) 253.314

**G at e** (B) 253.632

(C) 526.314

**G at e** (D) 526.632

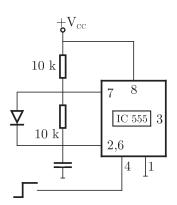

- **MCQ 8.46** IC 555 in the adjacent figure is configured as an astable multi-vibrator. It is enabled to to oscillate at t = 0 by applying a high input to pin 4. The pin description is : 1 and 8-supply; 2-trigger; 4-reset; 6-threshold 7-discharge. The waveform appearing across the capacitor starting from t = 0, as observed on a storage CRO is

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## CHAP 8

#### **PAGE 438**

#### **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

## **YEAR 2006**

## **ONE MARK**

#### ANALOG & DIGITAL ELECTRONICS

**PAGE 439**

## **YEAR 2006**

## **TWO MARKS**

**PAGE 440**

**MCQ 8.50** Consider the circuit shown in figure. If the  $\beta$  of the transistor is 30 and  $I_{CBO}$  is 20 mA and the input voltage is +5 V, the transistor would be operating in

**MCQ 8.52** A TTL NOT gate circuit is shown in figure. Assuming  $V_{BE} = 0.7$  V of both the transistors, if  $V_i = 3.0$  V, then the states of the two transistors will be

- (A)  $Q_1$  ON and  $Q_2$  OFF

- (B)  $Q_1$  reverse ON and  $Q_2$  OFF

- (C)  $Q_1$  reverse ON and  $Q_2$  ON

- (D)  $Q_1$  OFF and  $Q_2$  reverse ON

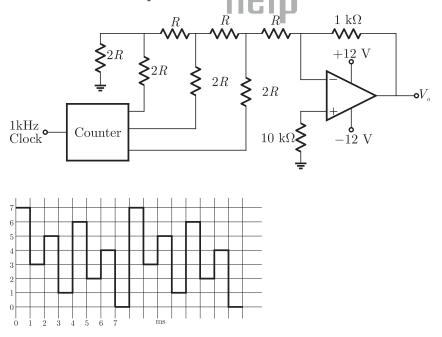

- **MCQ 8.53** A student has made a 3-bit binary down counter and connected to the R-2R ladder type DAC, [Gain  $= (-1 k\Omega/2R)$ ] as shown in figure to generate a staircase waveform. The output achieved is different as shown in figure. What could be the possible cause of this error ?

(A) The resistance values are incorrect option.

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |  |

|----------------------------------------------------------------|--|--|--|

| Published by: NODIA and COMPANY ISBN: 9788192276243            |  |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |  |

#### ANALOG & DIGITAL ELECTRONICS

(B) The counter is not working properly

**PAGE 442**

- (C) The connection from the counter of DAC is not proper

- (D) The R and 2R resistance are interchanged

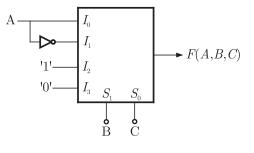

- **MCQ 8.54** A  $4 \times 1$  MUX is used to implement a 3-input Boolean function as shown in figure. The Boolean function F(A, B, C) implemented is

(A)  $F(A, B, C) = \Sigma(1, 2, 4, 6)$ (B)  $F(A, B, C) = \Sigma(1, 2, 6)$ (C)  $F(A, B, C) = \Sigma(2, 4, 5, 6)$ (D)  $F(A, B, C) = \Sigma(1, 5, 6)$

**MCQ 8.55** A software delay subroutine is written as given below :

| DELAY :   | MVI      | H, 255D                            |

|-----------|----------|------------------------------------|

|           | MVI      | L, 255D                            |

| LOOP :    | DCR      | L                                  |

|           | JNZ      | LOOP                               |

|           | DCR      |                                    |

|           | JNZ      | LOOP                               |

| How many  | times DC | R L instruction will be executed ? |

| (A) 255   |          | (B) 510                            |

| (C) 65025 |          | (D) 65279                          |

**MCQ 8.56** In an 8085 A microprocessor based system, it is desired to increment the contents of memory location whose address is available in (D,E) register pair and store the result in same location. The sequence of instruction is

| (A) XCHG  | (B) | XCHG  |

|-----------|-----|-------|

| INR M     |     | INX H |

| (C) INX D | (D) | INR M |

| XCHG      |     | XCHG  |

## **YEAR 2005**

#### **ONE MARK**

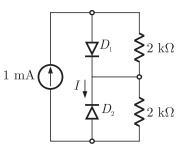

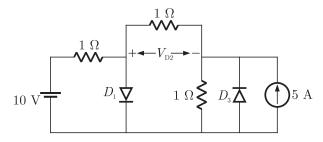

**MCQ 8.57** Assume that  $D_1$  and  $D_2$  in figure are ideal diodes. The value of current is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |  |

|----------------------------------------------------------------|---------------------|--|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |  |

| Visit us at: www.nodia.co.in                                   |                     |  |  |

#### **PAGE 443**

| (A) 0 mA | (B) $0.5 \text{ mA}$ |

|----------|----------------------|

| (C) 1 mA | (D) 2 mA             |

- **MCQ 8.58** The 8085 assembly language instruction that stores the content of H and L register into the memory locations  $2050_{\rm H}$  and  $2051_{\rm H}$ , respectively is (A) SPHL 2050<sub>H</sub> (B) SPHL 2051<sub>H</sub> (D) STAX 2050<sub>H</sub> (C) SHLD 2050<sub>H</sub>

- Assume that the N-channel MOSFET shown in the figure is ideal, and that **MCQ 8.59** its threshold voltage is +1.0 V the voltage  $V_{ab}$  between nodes a and b is

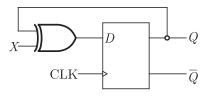

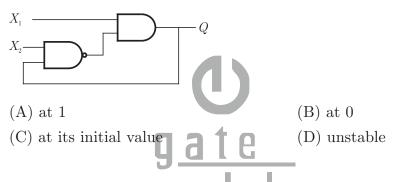

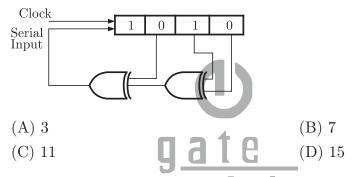

The digital circuit shown in the figure works as

(A) JK flip-flop (C) T flip-flop

(D) Ring counter

## **YEAR 2005**

**TWO MARKS**

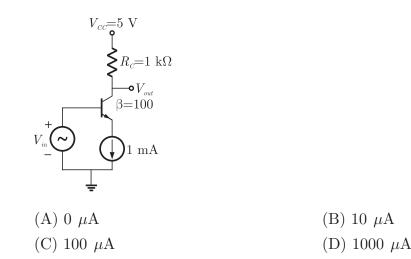

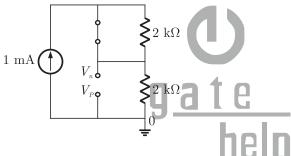

The common emitter amplifier shown in the figure is biased using a 1 mA MCQ 8.61 ideal current source. The approximate base current value is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |  |

|----------------------------------------------------------------|--|--|--|

| Published by: NODIA and COMPANY ISBN: 9788192276243            |  |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |  |

#### CHAP 8

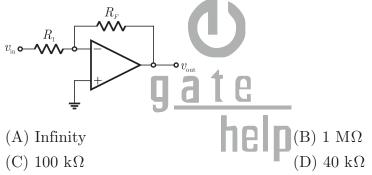

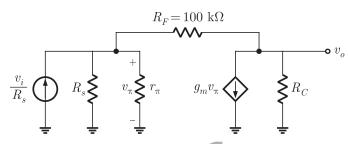

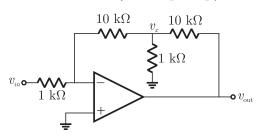

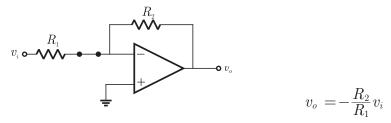

**MCQ 8.62** Consider the inverting amplifier, using an ideal operational amplifier shown in the figure. The designer wishes to realize the input resistance seen by the small-signal source to be as large as possible, while keeping the voltage gain between -10 and -25. The upper limit on  $R_F$  is 1 M $\Omega$ . The value of  $R_1$ should be

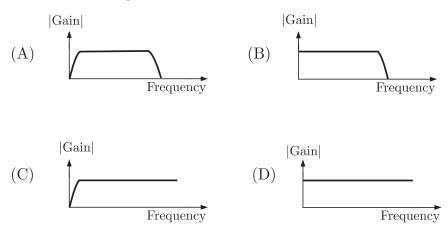

**MCQ 8.63** The typical frequency response of a two-stage direct coupled voltage amplifier is as shown in figure

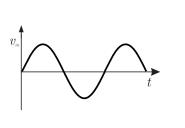

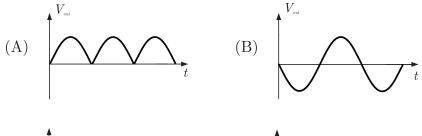

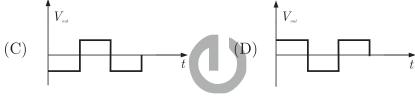

**MCQ 8.64** In the given figure, if the input is a sinusoidal signal, the output will appear as shown

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |  |

|----------------------------------------------------------------|--|--|--|

| Published by: NODIA and COMPANY ISBN: 9788192276243            |  |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |  |

| G | GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|---|----------------------------------------------------------------|---------------------|--|

|   | ublished by: NODIA and COMPANY                                 | ISBN: 9788192276243 |  |

| V | isit us at: www.nodia.co.in                                    |                     |  |

#### **ANALOG & DIGITAL ELECTRONICS**

#### CHAP 8

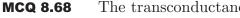

**MCQ 8.66**

**PAGE 446**

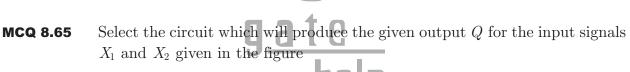

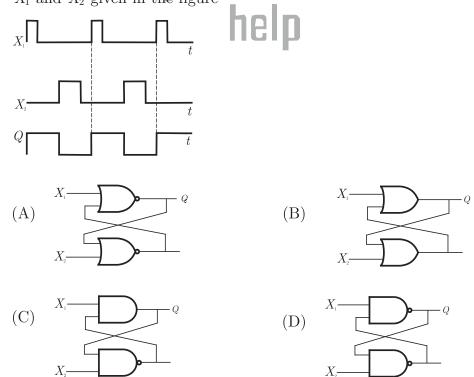

If  $X_1$  and  $X_2$  are the inputs to the circuit shown in the figure, the output Qis

MCQ 8.67

In the figure, as long as  $X_1 = 1$  and  $X_2 = 1$ , the output Q remains

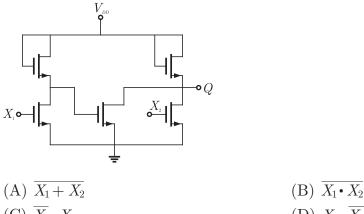

Data for Q. 68 and Q. 69 are given below. Solve the problems and choose the correct option.

Assume that the threshold voltage of the N-channel MOSFET shown in figure is + 0.75 V. The output characteristics of the MOSFET are also shown

The transconductance of the MOSFET is

- (A) 0.75 ms

- (C) 2 ms

(B) 1 ms(D) 10 ms

| CHAP 8   | ANALOG & DIGITAL ELECTRONICS         |           | <b>PAGE 447</b> |

|----------|--------------------------------------|-----------|-----------------|

|          |                                      |           |                 |

| MCQ 8.69 | The voltage gain of the amplifier is |           |                 |

|          | (A) + 5                              | (B) - 7.5 |                 |

|          | (C) + 10                             | (D) - 10  |                 |

## **YEAR 2004**

## **ONE MARK**

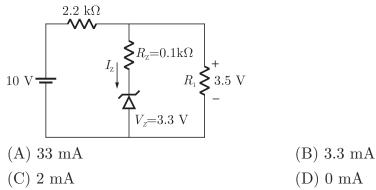

**MCQ 8.70** The current through the Zener diode in figure is

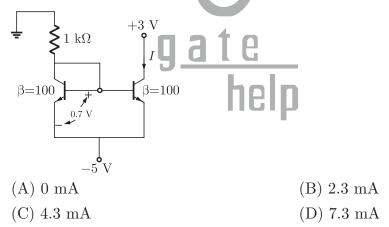

MCQ 8.71Two perfectly matched silicon transistor are connected as shown in figure.The value of the current I is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

#### **ANALOG & DIGITAL ELECTRONICS**

#### CHAP 8

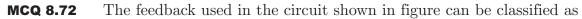

(A) shunt-series feedback

**PAGE 448**

(B) shunt-shunt feedback

(C) series-shunt feedback

(D) series-series feedback

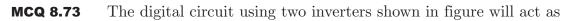

- (A) a bistable multi-vibrator

- (B) an astable multi-vibrator

- (C) a monostable multi-vibrator

- (D) an oscillator

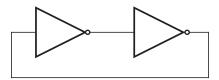

- **MCQ 8.74** The voltage comparator shown in figure can be used in the analog-to-digital conversion as

## **YEAR 2004**

## **TWO MARKS**

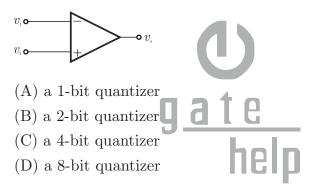

**MCQ 8.75** Assuming that the diodes are ideal in figure, the current in diode  $D_1$  is

**MCQ 8.76** The trans-conductance  $g_m$  of the transistor shown in figure is 10 mS. The value of the input resistance  $R_{in}$  is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

#### **PAGE 449**

**MCQ 8.77** The value of R for which the PMOS transistor in figure will be biased in linear region is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

## **ANALOG & DIGITAL ELECTRONICS**

#### CHAP 8

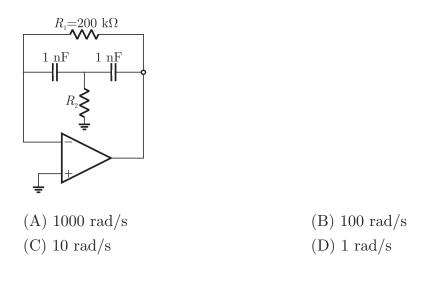

**MCQ 8.79** The input resistance  $R_{in} = v_x/i_x$  of the circuit in figure is

**MCQ 8.80** The simplified form of the Boolean expression  $Y = (\overline{A} \cdot BC + D)(\overline{A} \cdot D + \overline{B} \cdot \overline{C})$  can be written as

| (A) $\overline{A} \cdot D + \overline{B} \cdot \overline{C} \cdot D$ | (B) $AD + B \cdot \overline{C} \cdot D$            |

|----------------------------------------------------------------------|----------------------------------------------------|

| (C) $(\overline{A} + D)(\overline{B} \cdot C + \overline{D})$        | (D) $A \cdot \overline{D} + BC \cdot \overline{D}$ |

**MCQ 8.81** A digit circuit which compares two numbers  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  is shown in figure. To get output Y=0, choose one pair of correct input numbers.

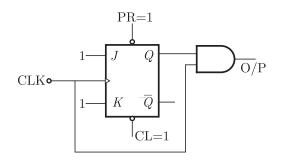

**MCQ 8.82** The digital circuit shown in figure generates a modified clock pulse at the output. Choose the correct output waveform from the options given below.

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## **PAGE 450**

**MCQ 8.84** In the Schmitt trigger circuit shown in figure, if  $V_{CE(sat)} = 0.1 \text{ V}$ , the output logic low level ( $V_{OL}$ ) is

| PAGE 452 |                      | ANALOG & DIGITAL ELECTRONICS | CHAP 8 |

|----------|----------------------|------------------------------|--------|

|          | (A) $1.25 \text{ V}$ | (B) $1.35 V$                 |        |

|          | (C) $2.50 \text{ V}$ | (D) 5.00 V                   |        |

**YEAR 2003**

## **ONE MARK**

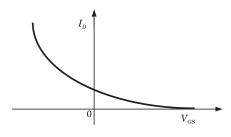

**MCQ 8.85** The variation of drain current with gate-to-source voltage  $(I_D - V_{GS}$  characteristic) of a MOSFET is shown in figure. The MOSFET is

- (A) an n-channel depletion mode device

- (B) an n-channel enhancement mode device

- (C) an p-channel depletion mode device

- (D) an p-channel enhancement mode device

- **MCQ 8.86** In the circuit of figure, assume that the transistor has  $h_{fe} = 99$  and  $V_{BE} = 0.7$  V. The value of collector current  $I_C$  of the transistor is approximately

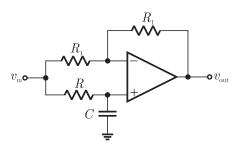

**MCQ 8.87** For the circuit of figure with an ideal operational amplifier, the maximum phase shift of the output  $v_{out}$  with reference to the input  $v_{in}$  is

| CHAP 8 |                    | ANALOG & DIGITAL ELECTRONICS | <b>PAGE 453</b> |

|--------|--------------------|------------------------------|-----------------|

|        | (A) 0°             | (B) $-90^{\circ}$            |                 |

|        | $(C) + 90^{\circ}$ | (D) $\pm 180^{\circ}$        |                 |

# **MCQ 8.88** Figure shows a 4 to 1 MUX to be used to implement the sum S of a 1-bit full adder with input bits P and Q and the carry input $C_{in}$ . Which of the following combinations of inputs to $I_0, I_1, I_2$ and $I_3$ of the MUX will realize the sum S?

$$\begin{array}{c|c}

I_{0} \\

I_{1} & 4:1 \\

I_{2} & \text{MUX} \\

I_{3} & S_{1} & S_{0} \\

\hline

P & Q

\end{array}$$

(A)

$$I_0 = I_1 = C_{in}; I_2 = I_3 = \overline{C}_{in}$$

(B)  $I_0 = I_1 = \overline{C}_{in}; I_2 = I_3 = C_{in}$

(C)  $I_0 = I_3 = C_{in}; I_1 = I_2 = \overline{C}_{in}$  (D)  $I_0 = I_3 = \overline{C}_{in}; I_1 = I_2 = C_{in}$

- MCQ 8.89 When a program is being executed in an 8085 microprocessor, its Program Counter contains

- (A) the number of instructions in the current program that have already been executed

- (B) the total number of instructions in the program being executed.

- (C) the memory address of the instruction that is being currently executed

- (D) the memory address of the instruction that is to be executed next

## YEAR 2003

# **MCQ 8.90** For the n-channel enhancement MOSFET shown in figure, the threshold voltage $V_{th} = 2$ V. The drain current $I_D$ of the MOSFET is 4 mA when the drain resistance $R_D$ is 1 k $\Omega$ . If the value of $R_D$ is increased to 4 k $\Omega$ , drain current $I_D$ will become

| (A) 2.8 mA | (B) 2.0 mA |

|------------|------------|

| (C) 1.4 mA | (D) 1.0 mA |

|            |            |

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

TWO MARKS

#### ANALOG & DIGITAL ELECTRONICS

#### CHAP 8

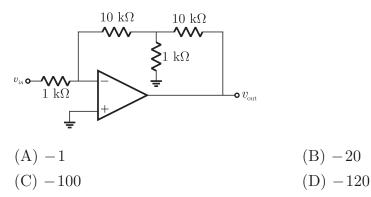

**MCQ 8.91** Assuming the operational amplifier to be ideal, the gain  $v_{out}/v_{in}$  for the circuit shown in figure is

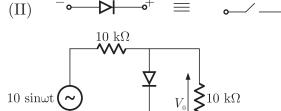

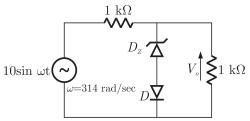

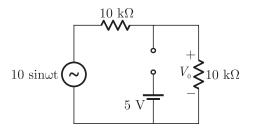

**MCQ 8.92** A voltage signal  $10 \sin \omega t$  is applied to the circuit with ideal diodes, as shown in figure, The maximum, and minimum values of the output waveform  $V_{out}$  of the circuit are respectively

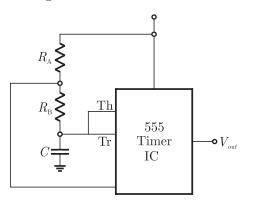

**MCQ 8.93** The circuit of figure shows a 555 Timer IC connected as an astable multivibrator. The value of the capacitor C is 10 nF. The values of the resistors  $R_A$  and  $R_B$  for a frequency of 10 kHz and a duty cycle of 0.75 for the output voltage waveform are

(A)

$$R_A = 3.62 \text{ k}\Omega, R_B = 3.62 \text{ k}\Omega$$

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## **PAGE 454**

# **CHAP 8**

#### **PAGE 455**

- (B)  $R_A = 3.62 \text{ k}\Omega, R_B = 7.25 \text{ k}\Omega$ (C)  $R_A = 7.25 \,\mathrm{k\Omega}, R_B = 3.62 \,\mathrm{k\Omega}$

- (D)  $R_A = 7.25 \,\mathrm{k}\Omega, R_B = 7.25 \,\mathrm{k}\Omega$

- The boolean expression  $\overline{X} Y \overline{Z} + \overline{XYZ} + XY\overline{Z} + XY\overline{Z} + XYZ$ can be **MCQ 8.94** simplified to (B)  $XY + \overline{Y}Z + Y\overline{Z}$ (A)  $X\overline{Z} + \overline{X}Z + YZ$ (D)  $\overline{XY} + Y\overline{Z} + \overline{XZ}$ (C)  $\overline{X}Y + YZ + XZ$

- **MCQ 8.95** The shift register shown in figure is initially loaded with the bit pattern 1010. Subsequently the shift register is clocked, and with each clock pulse the pattern gets shifted by one bit position to the right. With each shift, the bit at the serial input is pushed to the left most position (msb). After how many clock pulses will the content of the shift register become 1010 again?

An X-Y flip-flop, whose Characteristic Table is given below is to be **MCQ 8.96** implemented using a J-K flip flop **G**

| X | Y | $Q_{n+1}$        |

|---|---|------------------|

| 0 | 0 | 1                |

| 0 | 1 | $Q_n$            |

| 1 | 0 | $\overline{Q}_n$ |

| 1 | 1 | 0                |

| (A) $J = X, K = \overline{Y}$ | (B) $J = \overline{X}, K = Y$ |

|-------------------------------|-------------------------------|

| (C) $J = Y, K = \overline{X}$ | (D) $J = \overline{Y}, K = X$ |

**MCQ 8.97**

A memory system has a total of 8 memory chips each with 12 address lines and 4 data lines, The total size of the memory system is

(A) 16 kbytes (B) 32 kbytes (C) 48 kbytes (D) 64 kbytes

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                            |

|----------------------------------------------------------------|----------------------------|

| Published by: NODIA and COMPANY                                | <b>ISBN:</b> 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                            |

| <b>PAGE 456</b> | ANALOG & DIGITAL EL                                                                                                                                         | ECTRONICS CHA                     | <b>P</b> 8 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|

| MCQ 8.98        | The following program is written for<br>bytes located at memory addresses 1FI<br>LXI H, 1FFE<br>MOV B, M<br>INR L<br>MOV A, M<br>ADD B<br>INR L<br>MOV M, A | -                                 | two        |

|                 | XOR A<br>On completion of the execution of th                                                                                                               | e program, the result of addition | n is       |

|                 | found                                                                                                                                                       | e program, the result of addition |            |

|                 | (A) in the register A                                                                                                                                       | (B) at the memory address $100$   | 00         |

|                 | (C) at the memory address $1F00$                                                                                                                            | (D) at the memory address 200     | 00         |

# **YEAR 2002**

# **ONE MARK**

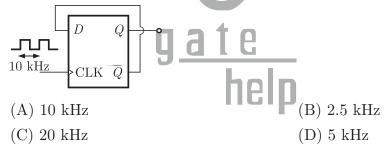

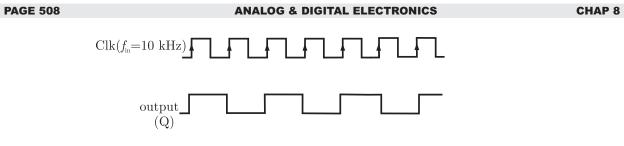

MCQ 8.99The frequency of the clock signal applied to the rising edge triggered D-flip-<br/>flop shown in Figure is 10 kHz. The frequency of the signal available at Q is.

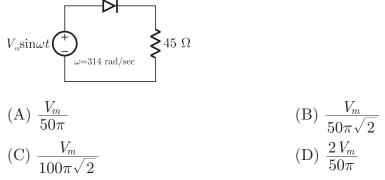

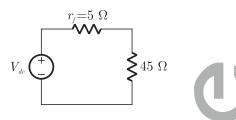

**MCQ 8.100** The forward resistance of the diode shown in Figure is  $5 \Omega$  and the remaining parameters are same at those of an ideal diode. The dc component of the source current is

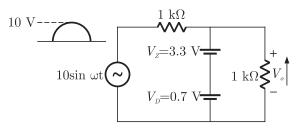

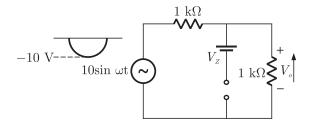

**MCQ 8.101** The cut-in voltage of both zener diode  $D_Z$  and diode D shown in Figure is 0.7 V, while break-down voltage of  $D_Z$  is 3.3 V and reverse break-down voltage of D is 50 V. The other parameters can be assumed to be the same

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

**CHAP 8**

as those of an ideal diode. The values of the peak output voltage ( $V_o$ ) are

- (A) 3.3 V in the positive half cycle and 1.4 V in the negative half cycle.

- (B) 4 V in the positive half cycle and 5 V in the negative half cycle.

- (C) 3.3 V in both positive and negative half cycles.

- (D) 4 V in both positive and negative half cycle

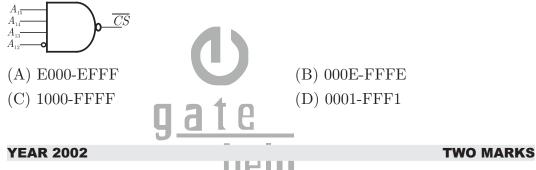

- The logic circuit used to generate the active low chip select ( $\overline{CS}$ ) by an 8085 MCQ 8.102 microprocessor to address a peripheral is shown in Figure. The peripheral will respond to addresses in the range.

- A first order, low pass filter is given with  $R = 50 \Omega$  and  $C = 5 \mu$ F. What is MCQ 8.103 the frequency at which the gain of the voltage transfer function of the filter is 0.25 ? (A) 4.92 kHz (B) 0.49 kHz

- (C) 2.46 kHz (D) 24.6 kHz

- The output voltage  $(v_a)$  of the Schmitt trigger shown in Figure swings **MCQ 8.104** between +15 V and -15 V. Assume that the operational amplifier is ideal. The output will change from +15 V to -15 V when the instantaneous value of the input sine wave is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

- (A) 5 V in the positive slope only (A)

- (B) 5 V in the negative slope only (B)

- (C) 5 V in the positive and negative slopes

- (D) 3 V in the positive and negative slopes.

- **MCQ 8.105** For the circuit shown in Figure, the boolean expression for the output Y in terms of inputs P, Q, R and S is

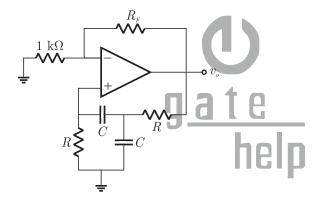

**MCQ 8.108** Value of resistance  $R_F$  is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

| ANALOG | & DIGITAL ELECTRONICS | 3 |

|--------|-----------------------|---|

|        |                       |   |

| (A) 110.9 k $\Omega$  | (B) 124.5 k $\Omega$ |

|-----------------------|----------------------|

| (C) 130.90 k $\Omega$ | (D) None of these    |

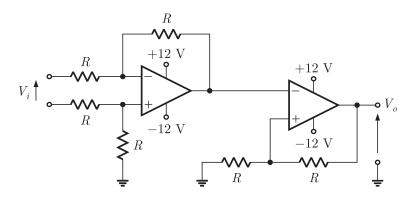

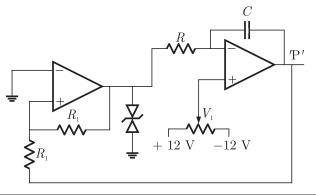

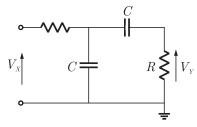

# Common data question Q.95-97\*.

The following network is used as a feedback circuit in an oscillator shown in figure to generate sinusoidal oscillations. Assuming that the operation amplifier is ideal.

given that  $R = 10 \text{ k}\Omega$  and C = 100 pF

**MCQ 8.109** The transfer function  $\frac{V_y}{V_x}$  of the first network is

| (A) $\frac{j\omega CR}{(1-\omega^2 R^2 C^2) + j3\omega CR}$ | (B) $\frac{j\omega CR}{(1-\omega^2 R^2 C^2) + j2\omega CR}$ |

|-------------------------------------------------------------|-------------------------------------------------------------|

| (C) $\frac{j\omega CR}{1+j3\omega CR}$                      | (D) $\frac{j\omega CR}{1+j2\omega CR}$                      |

| The frequency of oscillation will be                        |                                                             |

| (A) $\frac{1}{RC}$                                          | (B) $\frac{1}{2RC}$                                         |

| (C) $\frac{1}{4RC}$                                         | (D) None of these                                           |

| Value of $R_F$ is                                           |                                                             |

| (A) 1 k $\Omega$                                            | (B) 4 k $\Omega$                                            |

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

# CHAP 8

MCQ 8.110

MCQ 8.111

#### ANALOG & DIGITAL ELECTRONICS

#### CHAP 8

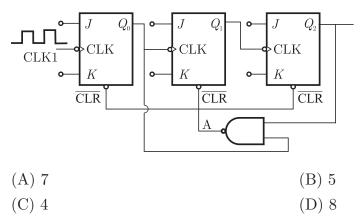

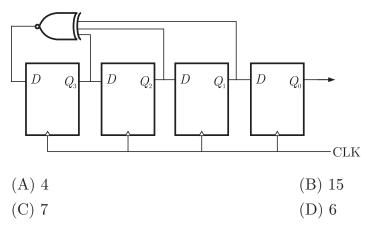

**MCQ 8.112** \*The ripple counter shown in figure is made up of negative edge triggered J-K flip-flops. The signal levels at J and K inputs of all the flip flops are maintained at logic 1. Assume all the outputs are cleared just prior to applying the clock signal.

module no. of the counter is:

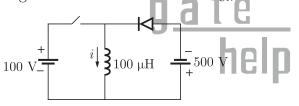

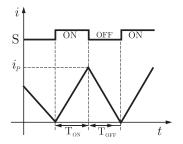

**MCQ 8.113** \*In Figure , the ideal switch S is switched on and off with a switching frequency f = 10 kHz. The switching time period is  $T = t_{ON} + t_{OFF} \mu s$ . The circuit is operated in steady state at the boundary of continuous and discontinuous conduction, so that the inductor current i is as shown in Figure. Values of the on-time  $t_{ON}$  of the switch and peak current  $i_p$ . are

(A) 63.33 μsec, 63.33 A

(C) 66.66 μsec, 66.66 mA

- (B)  $63.33 \ \mu sec$ ,  $63.33 \ \mu A$

- 66.66 mA

- (D) none of these

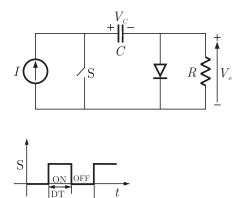

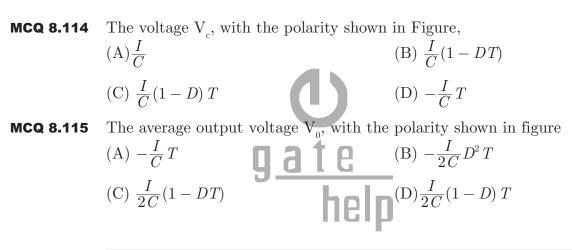

# Common Data Questions Q.114-115\*

In the circuit shown in Figure, the source I is a dc current source. The switch S is operated with a time period T and a duty ratio D. You may assume

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

## **PAGE 460**

## ANALOG & DIGITAL ELECTRONICS

#### **PAGE 461**

that the capacitance C has a finite value which is large enough so that the voltage.  $V_C$  has negligible ripple, calculate the following under steady state conditions, in terms of D, I and R

**CHAP 8**

# **YEAR 2001**

Published by: NODIA and COMPANY

Visit us at: www.nodia.co.in

**ONE MARK**

ISBN: 9788192276243

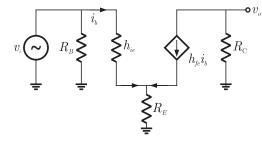

**MCQ 8.116** In the single-stage transistor amplifier circuit shown in Figure, the capacitor  $C_E$  is removed. Then, the ac small-signal mid-band voltage gain of the amplifier

#### **PAGE 462**

#### ANALOG & DIGITAL ELECTRONICS

#### CHAP 8

- **MCQ 8.117** Among the following four, the slowest ADC (analog-to-digital converter) is (A) parallel-comparator (i.e. flash) type

- (B) successive approximation type

- (C) integrating type

- (D) counting type

- **MCQ 8.118** The output of a logic gate is "1" when all its inputs are at logic "0". The gate is either

- (A) a NAND or an EX-OR gate

- (B) a NOR or an EX-OR gate

- (C) an AND or an EX-NOR gate

- (D) a NOR or an EX-NOR gate

- **MCQ 8.119** The output f of the 4-to-1 MUX shown in Figure is

MCQ 8.120 An op-amp has an open-loop gain of 10<sup>5</sup> and an open-loop upper cut-off frequency of 10 Hz. If this op-amp is connected as an amplifier with a closed-loop gain of 100, then the new upper cut-off frequency is

(A) 10 Hz

(B) 100 Hz

(C) 10 kHz

# **YEAR 2001**

# **TWO MARKS**

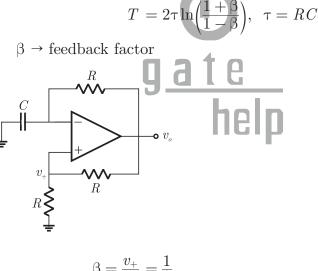

**MCQ 8.121** For the oscillator circuit shown in Figure, the expression for the time period of oscillation can be given by (where  $\tau = RC$ )

| CHAP 8 |                  | ANALOG & DIGITAL ELECTRONICS | <b>PAGE 463</b> |

|--------|------------------|------------------------------|-----------------|

|        | (A) $\tau \ln 3$ | (B) $2\tau \ln 3$            |                 |

|        | (C) $\tau \ln 2$ | (D) $2\tau \ln 2$            |                 |

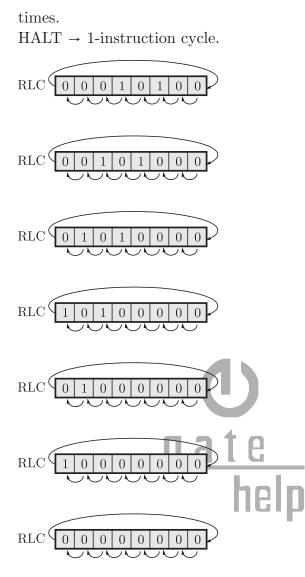

**MCQ 8.122** An Intel 8085 processor is executing the program given below.

|            | MVI A, $10 \text{ H}$   |

|------------|-------------------------|

|            | MVI B, $10 \text{ H}$   |

| BACK:      | NOP                     |

|            | ADD B                   |

|            | RLC                     |

|            | INC BACK                |

|            | HLT                     |

| umber of t | imes that the operation |

The number of times that the operation NOP will be executed is equal to (A) 1 (B) 2 (C) 3 (D) 4

**MCQ 8.123** A sample-and-hold (S/H) circuit, having a holding capacitor of 0.1 nF, is used at the input of an ADC (analog-to-digital converter). The conversion time of the ADC is  $1 \mu \sec$ , and during this time, the capacitor should not loose more than 0.5% of the charge put across it during the sampling time. The maximum value of the input signal to the S/H circuit is 5 V. The leakage current of the S/H circuit should be less than (A) 2.5 mA (C) 25.0  $\mu$ A

MCQ 8.124 An op-amp, having a slew rate of 62.8 V/μsec, is connected in a voltage follower configuration. If the maximum amplitude of the input sinusoidal is 10 V, then the minimum frequency at which the slew rate limited distortion would set in at the output is

(A) 1.0 MHz

(B) 6.28 MHz

| (C) 10.0 MHz | (D) 62.8 MHz |

|--------------|--------------|

**MCQ 8.125** An n-channel JFET, having a pinch off voltage  $(V_p)$  of -5 V, shows a transconductance  $(g_m)$  of 1 mA/V when the applied gate -to-source voltage  $(V_{GS})$  is -3 V. Its maximum transconductance (in mA/V) is (A) 1.5 (B) 2.0 (C) 2.5 (D) 3.0

**MCQ 8.126** \*The circuit shown in the figure is a MOD-N ring counter. Value of N is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

#### ANALOG & DIGITAL ELECTRONICS

CHAP 8

(assume initial state of the counter is 1110 i.e.  $Q_3 Q_2 Q_1 Q_0 = 1110$ ).

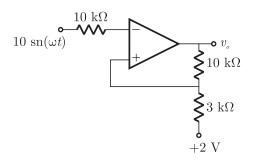

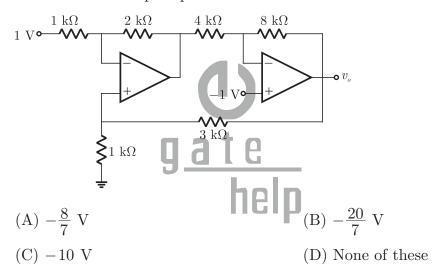

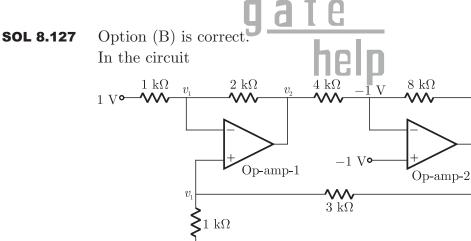

**MCQ 8.127** \*For the op-amp circuit shown in Figure, determine the output voltage  $v_o$ . Assume that the op-amps are ideal.

# Common Data Questions Q.128-129\*.

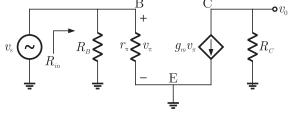

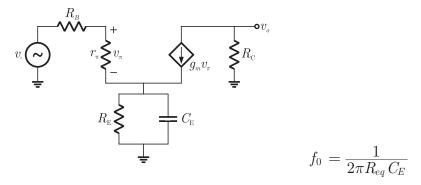

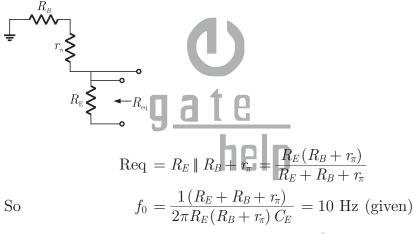

The transistor in the amplifier circuit shown in Figure is biased at  $I_c = 1 \text{ mA}$ Use  $V_T = kT/q = 26 \text{ mV}, \beta_0 = 200, r_b = 0, \text{ and } r_0 \rightarrow \infty$

| CHAP 8    | ANALOG & DIGITAL ELE                       | CTRONICS                  | <b>PAGE 465</b> |

|-----------|--------------------------------------------|---------------------------|-----------------|

| MCQ 8.128 | Small-signal mid-band voltage gain $v_o/a$ | $v_i$ is                  |                 |

|           | (A) - 8                                    | (B) 38.46                 |                 |

|           | (C) - 6.62                                 | (D) $-1$                  |                 |

| MCQ 8.129 | What is the required value of $C_E$ for    | the circuit to have a low | ver cut-off     |

**MCQ 8.129** What is the required value of  $C_E$  for the circuit to have a lower cut-off frequency of 10 Hz (A) 0.15 mF (B) 1.59 mF

| $\langle \rangle$ |                  |                      |

|-------------------|------------------|----------------------|

| (C)               | $5 \ \mu { m F}$ | (D) 10 $\mu {\rm F}$ |

# Common Data Questions Q.130-131\*

For the circuit shown in figure

**MCQ 8.131** If the above filter has a 3 dB frequency of 1 kHz, a high frequency input resistance of 100 k $\Omega$  and a high frequency gain of magnitude 10. Then values of  $R_1$ ,  $R_2$  and C respectively are :-

- (A) 100 k $\Omega,$  1000 k $\Omega,$  15.9 nF

- (B) 10 k\Omega, 100 k\Omega, 0.11  $\mu F$

- (C) 100 k $\Omega,$  1000 k $\Omega,$  15.9 nF

- (D) none of these

\*\*\*\*\*\*\*\*

**SOL 8.3**

**о**-В

# **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

# SOLUTION

**SOL 8.1** Option (A) is correct.

Prime implicants are the terms that we get by solving K-map

SOL 8.2Option (D) is correct.Let v > 0.7 V and diode is forward biased. Applying Kirchoff's voltage law

$$10 - i \times 1k - v = 0$$

$$10 - \left[\frac{v - 0.7}{500}\right](1000) - v = 0$$

$$10 - (v - 0.7) \times 2 - v = 0$$

$$v = \frac{11.4}{3} = 3.8 \text{ V} > 0.7 \quad \text{(Assumption is true)}$$

So,

$$i = \frac{v - 0.7}{500} = \frac{3.8 - 0.7}{500} = 6.2 \text{ mA}$$

Option (B) is correct.

Y = 1, when A > B

$A = a_1 a_0, \ B = b_1 b_0$

|       |       |       | - •,  |   |

|-------|-------|-------|-------|---|

| $a_1$ | $a_0$ | $b_1$ | $b_0$ | Y |

| 0     | 1     | 0     | 0     | 1 |

| 1     | 0     | 0     | 0     | 1 |

| 1     | 0     | 0     | 1     | 1 |

| 1     | 1     | 0     | 0     | 1 |

| 1     | 1     | 0     | 1     | 1 |

| 1     | 1     | 1     | 0     | 1 |

Total combination = 6

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

SOL 8.4 Option (A) is correct. The given circuit is

Condition for the race-around

It occurs when the output of the circuit  $(Y_1, Y_2)$  oscillates between '0' and '1' checking it from the options.

**1.** Option (A): When CLK = 0

Output of the NAND gate will be  $A_1 = B_1 = \overline{0} = 1$ . Due to these input to the next NAND gate,  $Y_2 = \overline{Y_1 \cdot 1} = \overline{Y_1}$  and  $Y_1 = \overline{Y_2 \cdot 1} = \overline{Y_2}$ .

If  $Y_1 = 0$ ,  $Y_2 = \overline{Y_1} = 1$  and it will remain the same and doesn't oscillate. If  $Y_2 = 0$ ,  $Y_1 = \overline{Y_2} = 1$  and it will also remain the same for the clock period. So, it won't oscillate for CLK = 0.

So, here race around doesn't occur for the condition CLK = 0.

**2.** Option (C): When CLK = 1, A = B = 1

$A_1 = B_1 = 0$  and so  $Y_1 = Y_2 = 1$ And it will remain same for the clock period. So race around doesn't occur for the condition.

**3.** Option (D): When CLK = 1, A = B = 0So,  $A_1 = B_1 = 1$

And again as described for Option (B) race around doesn't occur for the condition.

So, Option (A) will be correct.

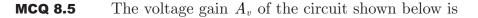

SOL 8.5Option (D) is correct.DC Analysis :

Using KVL in input loop,

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

$$V_{C} - 100I_{B} - 0.7 = 0$$

$$V_{C} = 100I_{B} + 0.7 \qquad \dots(i)$$

$$I_{C} \simeq I_{E} = \frac{13.7 - V_{C}}{12k} = (\beta + 1)I_{B}$$

$$\frac{13.7 - V_{C}}{12 \times 10^{3}} = 100I_{B} \qquad \dots(ii)$$

Solving equation (i) and (ii),

$I_B = 0.01 \,\mathrm{mA}$

# Small Signal Analysis :

Transforming given input voltage source into equivalent current source.

This is a shunt-shunt feedback amplifier. Given parameters,

$$r_{\pi} = \frac{V_T}{I_B} = \frac{25 \text{ mV}}{0.01 \text{ mA}} = 2.5 \text{ k}\Omega$$

$$g_m = \frac{\beta}{r_{\pi}} = \frac{100}{2.5 \times 1000} = 0.04 \text{ s}$$

Writing KCL at output node

$$rac{v_0}{R_C} + g_m v_\pi + rac{v_0 - v_\pi}{R_F} = 0$$

$$v_0 \left[ \frac{1}{R_C} + \frac{1}{R_F} \right] + v_\pi \left[ g_m - \frac{1}{R_F} \right] = 0$$

Substituting  $R_C = 12 \text{ k}\Omega$ ,  $R_F = 100 \text{ k}\Omega$ ,  $g_m = 0.04 \text{ s}$

$$v_0(9.33 imes 10^{-5}) + v_\pi(0.04) = 0$$

$$v_0 = -428.72 V_{\pi}$$

....(i)

Writing KCL at input node

$$\frac{v_i}{R_s} = \frac{v_\pi}{R_s} + \frac{v_\pi}{r_\pi} + \frac{v_\pi - v_o}{R_F} = v_\pi \Big[ \frac{1}{R_s} + \frac{1}{r_\pi} + \frac{1}{R_F} \Big] - \frac{v_0}{R_F}$$

$$= v_\pi (5.1 \times 10^{-4}) - \frac{v_0}{R_F}$$

Substituting  $V_{\pi}$  from equation (i)

$$\frac{v_i}{R_s} = \frac{-5.1 \times 10^{-4}}{428.72} v_0 - \frac{v_0}{R_F}$$

$\frac{v_i}{10 \times 10^3} = -1.16 \times 10^{-6} v_0 - 1 \times 10^{-5} v_0 R_s = 10 \text{ k}\Omega \text{ (source resistance)}$

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

$$\frac{v_i}{10 \times 10^3} = -1.116 \times 10^{-5}$$

$$|A_v| = \left|\frac{v_0}{v_i}\right| = \frac{1}{10 \times 10^3 \times 1.116 \times 10^{-5}} \simeq 8.96$$

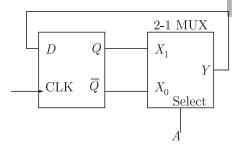

**SOL 8.6** Option (D) is correct.

Let  $Q_{n+1}$  is next state and  $Q_n$  is the present state. From the given below figure.

$$D = Y = \overline{A}X_0 + AX_1$$

$$Q_{n+1} = D = \overline{A}X_0 + AX_1$$

$$Q_{n+1} = \overline{A} \ \overline{Q_n} + AQ_n$$

$$A = 0,$$

$$A = 1,$$

$$Q_{n+1} = \overline{Q_n}$$

$$Q_{n+1} = Q_n$$

(toggle of previous state)

(toggle of previous state)

So state diagram is

If If

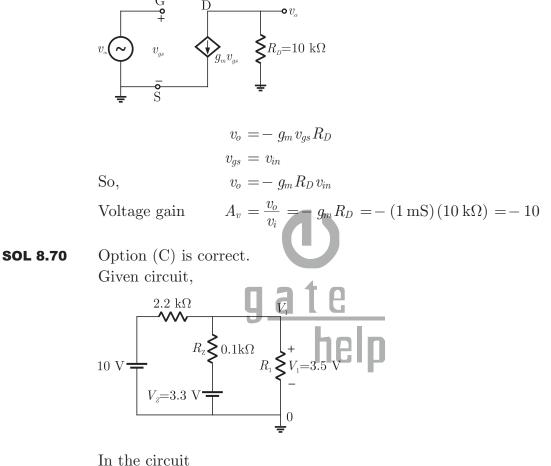

Option (B) is correct. **SOL 8.7** First we obtain the transfer function.

$$\frac{0 - V_i(j\omega)}{\frac{1}{j\omega C} + R_1} + \frac{0 - V_o(j\omega)}{R_2} = 0$$

$$\frac{V_o(j\omega)}{R_2} = \frac{-V_i(j\omega)}{1}$$

$$\frac{1}{R_2} = \frac{1}{\frac{1}{j\omega C} + R_1}$$

$$V_o(j\omega) = -rac{V_i(j\omega)R_2}{R_1 - jrac{1}{\omega C}}$$

$\frac{1}{\omega C} \to \infty$ , so  $V_o = 0$ At  $\omega \to 0$  (Low frequencies),  $\frac{1}{\omega C} \rightarrow 0$ , so  $V_o(j\omega) = -\frac{R_2}{R_1} V_i(j\omega)$ At  $\omega \to \infty$  (higher frequencies),

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

# **ANALOG & DIGITAL ELECTRONICS**

The filter passes high frequencies so it is a high pass filter.

$$H(j\omega) = \frac{V_o}{V_i} = \frac{-R_2}{R_1 - j\frac{1}{\omega C}}$$

$$|H(\infty)| = \left|\frac{-R_2}{R_1}\right| = \frac{R_2}{R_1}$$

At 3 dB frequency, gain will be  $\sqrt{2}\,$  times of maximum gain  $[H(\infty)]$

$$|H(j\omega_0)| = \frac{1}{\sqrt{2}} |H(\infty)|$$

$$\frac{R_2}{\sqrt{2}} = \frac{1}{\sqrt{2}} \left(\frac{R_2}{R}\right)$$

So,

$$\sqrt{R_1^2 + \frac{1}{\omega_0^2 C^2}} \quad \sqrt{2(R_1)}$$

$$2R_1^2 = R_1^2 + \frac{1}{\omega_0^2 C^2} \Rightarrow R_1^2 = \frac{1}{\omega^2 C^2}$$

$$\omega_0 = \frac{1}{R_1 C}$$

So, it will act as a Band pass filter.

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

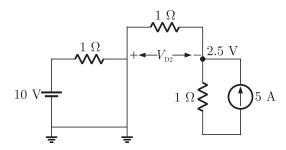

# **SOL 8.9** Option (D) is correct.

The first half of the circuit is a differential amplifier (negative feedback)  $V_a = - (V_i)$

Second op-amp has a positive feedback, so it acts as an schmitt trigger. Since

$V_a = -V_i$  this is a non-inverting schmitt trigger.

Threshold value

**SOL 8.11** Option (C) is correct. LXI D, DISP LP : CALL SUB LP + 3 When CALL SUB is executed LP+3 value is pushed(inserted) in the stack. POP H  $\Rightarrow$  HL = LP + 3 DAD D  $\Rightarrow$  HL = HL + DE

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |

|----------------------------------------------------------------|---------------------|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |

| Visit us at: www.nodia.co.in                                   |                     |

= LP + 3 + DE

PUSH H  $\Rightarrow$  The last two value of the stack will be HL value i.e, LP + DISP + 3

SOL 8.12 Option (D) is correct. Zener Diode is used as stabilizer. The circuit is assumed to be as

We can see that both BE and BC Junction are forwarded biased. So the BJT is operating in saturation.

Collector current  $I_C = \frac{12 - 0.2}{2.2k} = 5.36 \text{ mA}$ *Note:*- In saturation mode  $I_C \neq \beta I_B$

Option (C) is correct. **SOL 8.13**

The characteristics equation of the JK flip-flop is

$Q_{n+1} = J\overline{Q}_n + \overline{K}Q_n$

$Q_{n+1}$  is the next state

From figure it is clear that

$$J = \overline{Q_B}; K = Q_B$$

The output of JK flip flop

$$Q_{A(n+1)} = \overline{Q_B} \, \overline{Q_A} + \overline{Q_B} \, Q_A = \overline{Q_B} (\overline{Q_A} + Q_A) = \overline{Q_B}$$

Output of T flip-flop 6

$$Q_{B(n+1)} = Q_A$$

| Clock pulse       | $Q_A$ | $Q_B$ | $Q_{A(n+1)}$ | $Q_{B(n+1)}$ |

|-------------------|-------|-------|--------------|--------------|

| Initially $(t_n)$ | 1     | 0     | 1            | 0            |

| $t_n + 1$         | 1     | 0     | 1            | 0            |

| $t_n + 2$         | 1     | 0     | 1            | 0            |

| $t_n + 3$         | 1     | 0     | 1            | 0            |

#### **ANALOG & DIGITAL ELECTRONICS**

#### **PAGE 473**

# **SOL 8.14** Option (C) is correct.

We can obtain three operating regions depending on whether the Zener and PN diodes are forward biased or reversed biased.

1.  $v_i \leq -0.7 \text{ V}$ , zener diode becomes forward biased and diode D will be off so the equivalent circuit looks like

The output  $v_o = -0.7 \text{ V}$ 2. When  $-0.7 < v_i \le 5.7$ , both zener and diode *D* will be off. The circuit is

Note that zener goes in reverse breakdown(i.e acts as a constant battery) only when difference between its p-n junction voltages exceeds 10 V. 3. When  $v_i > 5.7$  V, the diode D will be forward biased and zener remains off, the equivalent circuit is

$v_o = 5 + 0.7 = 5.7 \text{ V}$

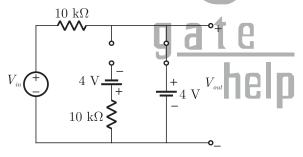

# **SOL 8.15** Option (B) is correct. Since the op-amp is ideal

$$v_{+} = v_{-} = +2$$

volt

By writing node equation

$$\frac{v_{-}-0}{R} + \frac{v_{-}-v_{o}}{2R} = 0$$

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

$$\frac{2}{R} + \frac{(2 - v_o)}{2R} = 0$$

$$4 + 2 - v_o = 0$$

$$v_o = 6 \text{ volt}$$

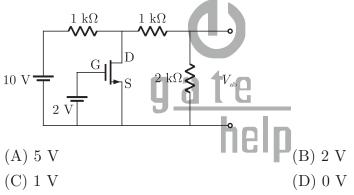

**SOL 8.16** Option (B) is correct. Given circuit is,

We can observe that diode  $D_2$  is always off, whether  $D_1$ , is on or off. So equivalent circuit is.

$D_1$  is ON in this condition and

$$V_0 = \frac{10}{10 + 10} \times 10$$

$$= 5 \text{ volt}$$

**SOL 8.17** Option (A) is correct.

By writing KVL equation for input loop (Base emitter loop)

$$10 - (10 \,\mathrm{k}\Omega) \,I_B - V_{BE} - V_0 = 0 \qquad \dots (1)$$

Emitter current  $I_E = \frac{V_0}{100}$

So,

$$egin{aligned} I_C &\simeq I_E = eta I_B \ rac{V_0}{100} &= 100 I_B \ I_B &= rac{V_0}{10 imes 10^3} \end{aligned}$$

Put  $I_B$  into equation (1)

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |

|----------------------------------------------------------------|--|--|

| Published by: NODIA and COMPANY ISBN: 978819227624             |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |

$$10 - (10 \times 10^3) \frac{V_0}{10 \times 10^3} - 0.7 - V_0 = 0$$

9.3 - 2 V\_0 = 0

$V_0 = \frac{9.3}{2} = 4.65 \text{ A}$

**SOL 8.18** Option (A) is correct. The circuit is

$\Rightarrow$

Output Y is written as

$Y = X \oplus B$

Since each gate has a propagation delay of 10 ns.

**SOL 8.19** Option (D) is correct. CALL, Address performs two operations (1) PUSH PC  $\Rightarrow$  Save the contents of PC (Program Counter) into stack. SP = SP - 2 (decrement) ((SP))  $\leftarrow$  (PC) (2) Addr stored in PC. (PC)  $\leftarrow$  Addr

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

#### **ANALOG & DIGITAL ELECTRONICS**

CHAP 8

**SOL 8.20**Option (B) is correct.Function F can be minimized by grouping of all 1's in K-map as following.

| X $X$ $X$ $X$ | 2 00 | 01 | 11 | 10 |

|---------------|------|----|----|----|

| 0             | 1    | 1  | 1  | 0  |

| 1             | 0    | 0  | 1  | 0  |

$$F = \overline{X} \ \overline{Y} + \ YZ$$

**SOL 8.21** Option (D) is correct. Since  $F = \overline{X} \ \overline{Y} + YZ$ In option (D)

- **SOL 8.22** Option (A) is correct. **A Contract Co**

- SOL 8.23 Option (B) is correct. The increasing order of speed is as following Magnetic tape> CD-ROM> Dynamic RAM>Cache Memory>Processor register

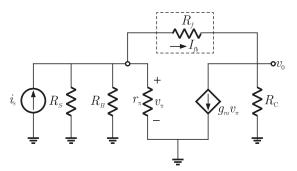

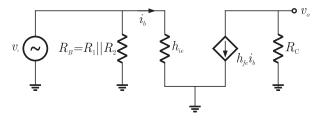

**SOL 8.24** Option (B) is correct. Equivalent circuit of given amplifier

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

## **PAGE 476**

| CHAP 8   | ANALOG & DIGITAL ELECTRONICS PAGE 4                                                                                                                        | 77 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | Feedback samples output voltage and adds a negative feedback voltage ( $v$ to input.                                                                       | )  |

|          | So, it is a voltage-voltage feedback.                                                                                                                      |    |

| SOL 8.25 | Option () is correct.<br>NOR and NAND gates considered as universal gates.                                                                                 |    |

| SOL 8.26 | Option (A) is correct.<br>Let voltages at positive and negative terminals of op-amp are $V_+$ and<br>respectively, then<br>$V_+ = V = V_s$ (ideal op-amp)  | V  |

|          | In the circuit we have,<br>$\frac{V-0}{\left(\frac{1}{Cs}\right)} + \frac{V-V_0(s)}{R} = 0$                                                                |    |

|          | $(RCs) V + V - V_0(s) = 0$                                                                                                                                 |    |

|          | $(1 + RCs) V_s = V_0(s)$<br>Similarly current $I_s$ is, $I_s = \frac{V_s - V_0}{R}$                                                                        |    |

|          | $I_{s} = \frac{RCs}{R} V_{s}$ $I_{s} = j\omega CV_{s}$ $I_{s} =  \omega CV_{s}  \angle + 90^{\circ}$ $ I_{s}  = 2\pi f \times 10 \times 10^{-6} \times 10$ |    |

|          | $ I_s  = 2 \times \pi \times 50 \times 10^{-6} \times 10^{-6}$                                                                                             |    |

|          | $ I_s  = 10\pi$ mA, leading by 90°                                                                                                                         |    |

| SOL 8.27 | Option (D) is correct.<br>Input and output power of a transformer is same<br>$P_{in} = P_{out}$                                                            |    |

|          | for emitter follower, voltage $gain(A_v) = 1$<br>current $gain(A_i) > 1$                                                                                   |    |

|          | Power $(P_{out}) = A_v A_i P_{in}$<br>Since emitter follower has a high current gain so $P_{out} > P_{in}$                                                 |    |

| SOL 8.28 | Option (D) is correct.<br>For the given instruction set,<br>XRA $A \Rightarrow$ XOR $A$ with $A \Rightarrow A = 0$                                         |    |

| _        | MVI $B$ , F0 H $\Rightarrow$ $B =$ F0 H                                                                                                                    |    |

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

SUB

$$B \Rightarrow A = A - B$$

$A = 000000000$

$B = 11110000$

2's complement of  $(-B) = 00010000$

$A + (-B) = A - B = 00010000$

$= 10 \,\text{H}$

SOL 8.29 Option (D) is correct.

This is a schmitt trigger circuit, output can takes two states only.

$$V_{OH} = + 6$$

volt

$V_{OL} = - 3$  volt

Threshold voltages at non-inverting terminals of op-amp is given as

$$\frac{V_{TH} - 6}{2} + \frac{V_{TH} - 0}{1} = 0$$

$$3 V_{TH} - 6 = 0$$

$$V_{TH} = 2 V \text{ (Upper threshold)}$$

Similarly

$$\frac{V_{TL} - (-3)}{2} + \frac{V_{TL}}{1} = 0$$

$$3 V_{TL} + 3 = 0$$

$$V_{TL} = -1 V \text{ (Lower threshold)}$$

For

$$V_{in} < 2 \text{ Volt}, V_0 = +6 \text{ Volt}$$

$$V_{in} > 2 \text{ Volt}, V_0 = -3 \text{ Volt}$$

For

$$V_{in} < -1$$

Volt  $V_0 = +6$  Volt

$$V_{in} > -1$$

Volt  $V_0 = -3$  Volt

Output waveform

Output voltage  $V_0 = \frac{10\sin\omega t}{10+10} \times 10 = 5\sin\omega t$

Due to resistor divider, voltage across diode  $V_D < 0$  (always). So it in reverse bias for given input.

Output,  $V_0 = 5 \sin \omega t$

**SOL 8.31** Option (C) is correct.

Diode  $D_1$  is forward biased.

So, current *I* is,  $I = I_{C2} = I_{C1}$  $= \frac{0 - (-4.3)}{1} = 4.3 \text{ mA}$

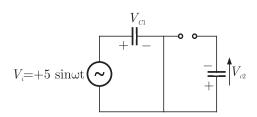

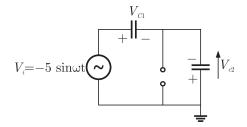

**SOL 8.32** Option (D) is correct. In positive half cycle of input, diode  $D_1$  is in forward bias and  $D_2$  is off, the equivalent circuit is

Capacitor  $C_1$  will charge up to +5 volt.  $V_{C_1} = +5$  volt

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

## **ANALOG & DIGITAL ELECTRONICS**

In negative halt cycle diode  $D_1$  is off and  $D_2$  is on.

Now capacitor  $V_{C2}$  will charge upto -10 volt in opposite direction.

**SOL 8.33** Option () is correct.

Let input  $V_{in}$  is a sine wave shown below

According to given transfer characteristics of rectifiers output of rectifier P is.

Similarly output of rectifier Q is

Output of a full wave rectifier is given as

To get output  $V_0$

$V_0 = K(-V_P + V_Q)$  K – gain of op-amp

So, P should connected at inverting terminal of op-amp and Q with non-inverting terminal.

- **SOL 8.34** Option () is correct.

- **SOL 8.35** Option (C) is correct. For low frequencies,  $\omega \to 0$ , so  $\frac{1}{\omega C} \to \infty$ Equivalent circuit is,  $v_i \bullet R_1 \bullet v_a \bullet v_$

Applying node equation at positive and negative input terminals of op-amp.

$$\frac{v_A - v_i}{R_1} + \frac{v_A - v_o}{R_2} = 0$$

2 $v_A = v_i + v_o$ ,  $\therefore R_1 = R_2 = R_A$

Similarly,

$$\frac{v_A - v_i}{R_3} + \frac{v_A - 0}{R_4} = 0$$

2 $v_A = v_{in},$   $\therefore R_3 = R_4 = R_B$

So,  $v_o = 0$

It will stop low frequency signals. For high frequencies,

$$\omega \to \infty$$

, then  $\frac{1}{\omega C} \to 0$

Equivalent circuit is,

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

#### **ANALOG & DIGITAL ELECTRONICS**

Output,  $v_o = v_i$ So it will pass high frequency signal. This is a high pass filter.

SOL 8.36 Option (D) is correct.

In Q.7.21 cutoff frequency of high pass filter is given by,

$$\omega_h = \frac{1}{2\pi R_A C}$$

Here given circuit is a low pass filter with cutoff frequency,

$$\omega_L = \frac{1}{2\pi \frac{R_A}{2}C} = \frac{2}{2\pi R_A C}$$

$$\omega_L = 2\omega_h$$

When both the circuits are connected together, equivalent circuit is,

$$\stackrel{\text{I/P}}{\longrightarrow} \stackrel{\text{High pass}}{\text{filter } (\omega_h)} \stackrel{\text{Low pass}}{\longrightarrow} \stackrel{\text{O/P}}{\text{filter } (2\omega_h)} \stackrel{\text{O/P}}{\longleftarrow}$$

So this is Band pass filter, amplitude response is given by.

**SOL 8.37** Option (B) is correct. In SOP form, F is written as

$$F = \Sigma m (1, 3, 5, 6)$$

=  $\overline{X} \ \overline{Y}Z + \overline{X} \ YZ + X \overline{Y}Z + X \overline{Y}Z$

Solving from K- map

$$I_{B(\text{sat})} = \frac{I_{C(\text{sat})}}{\beta} = \frac{5}{100} = .050 \text{ mA}$$

$I_B < I_{B(sat)}$ , so transistor is in forward active region.

#### **ANALOG & DIGITAL ELECTRONICS**

SOL 8.40 Option (B) is correct. In the circuit

We can analyze that the transistor is operating in active region.

$$V_{BE(ON)} = 0.6$$

volt

$V_B - V_E = 0.6$

$6.6 - V_E = 0.6$

$V_E = 6.6 - 0.6 = 6$  volt

At emitter (by applying KCL),

$$I_E = I_B + I_L$$

$I_E = \frac{6 - 6.6}{1 \,\mathrm{k}\Omega} + \frac{6}{10 \,\Omega} \simeq 0.6 \,\mathrm{amp}$

$V_{CE} = V_C - V_E = 10 - 6 = 4$  volt Power dissipated in transistor is given by.

Ì

$$P_T = \frac{V_{CE} \times I_C}{2.4 \text{ W}} \stackrel{I_C}{=} \frac{1}{2.4 \text{ W}} \stackrel{I_C}{=}$$

$\therefore I_C \simeq I_E = 0.6 \text{ amp}$

# **SOL 8.41** Option (D) is correct.

This is a voltage-to-current converter circuit. Output current depends on input voltage.

Since op-amp is ideal  $v_+ = v_- = v_1$ Writing node equation.

$$\frac{v_1 - v}{R_1} + \frac{v_1 - 0}{R_2} = 0$$

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

#### **ANALOG & DIGITAL ELECTRONICS**

$$\left(\frac{R_1 + R_2}{R_1 R_2}\right) = \frac{V}{R_1}$$

$$v_1 = V\left(\frac{R_2}{R_1 + R_2}\right)$$

Since the op-amp is ideal therefore

$v_1$

$$i_L = i_1 = rac{v_1}{r} = rac{V}{r} \Big( rac{R_2}{R_1 + R_2} \Big)$$

**SOL 8.42**Option (D) is correct.In the circuit output Y is given as

$$Y = [A \oplus B] \oplus [C \oplus D]$$

Output Y will be 1 if no. of 1's in the input is odd.

**SOL 8.43** Option () is correct.

This is a class-B amplifier whose efficiency is given as

$$\eta = \frac{\pi}{4} \frac{V_P}{V_{CC}}$$

where  $V_P \rightarrow$  peak value of input signal

$V_{CC} \rightarrow$  supply voltage

here  $V_P = 7$  volt,  $V_{CC} = 10$  volt

so,

$$g_{\pi} = \frac{\pi}{4} \frac{27}{10} \times 100 = 54.95\% \simeq 55\%$$

**SOL 8.44** Option (B) is correct.

In the circuit the capacitor starts charging from 0 V (as switch was initially closed) towards a steady state value of 20 V.

So at any time t, voltage across capacitor (i.e. at inverting terminal of opamp) is given by

$$egin{aligned} v_c(t) &= v_c(\infty) + \left[ v_c(0) - v_c(\infty)

ight] e^{rac{-t}{RC}} \ v_c(t) &= 20 \left( 1 - e^{rac{-t}{RC}}

ight) \end{aligned}$$

Voltage at positive terminal of op-amp

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |

|----------------------------------------------------------------|--|--|

| Published by: NODIA and COMPANY ISBN: 9788192276243            |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |

**PAGE 485**

#### **ANALOG & DIGITAL ELECTRONICS**

$$\frac{v_{+} - v_{out}}{10} + \frac{v_{+} - 0}{100} = 0$$

$$v_{+} = \frac{10}{11}v_{out}$$

Due to zener diodes,  $-5 \le v_{out} \le +5$ So,  $v_+ = \frac{10}{11}(5)$  V

Transistor form -5 V to +5 V occurs when capacitor charges up to  $v_+$ .

So

$$20(1 - e^{-t/RC}) = \frac{10 \times 5}{11}$$

$$1 - e^{-t/RC} = \frac{5}{22}$$

$$\frac{17}{22} = e^{-t/RC}$$

$$t = RC \ln\left(\frac{22}{17}\right) = 1 \times 10^3 \times .01 \times 10^{-6} \times 0.257 = 2.57 \ \mu \text{sec}$$

Voltage waveforms in the circuit is shown below

**SOL 8.45**Option (B) is correct.First convert the given number from hexadecimal to its binary equivalent,<br/>then binary to octal.Hexadecimal no.AB. CDBinary equivalent $\frac{1010}{A}$  $\frac{1011}{B}$  $\frac{1101}{D}$

To convert in octal group three binary digits together as shown  $\underbrace{010}_{2} \underbrace{101}_{5} \underbrace{011}_{3} \cdot \underbrace{110}_{6} \underbrace{011}_{3} \underbrace{010}_{2}$

So,  $(AB.CD)_{\rm H} = (253.632)_8$

# **SOL 8.46** Option (B) is correct.

In a 555 astable multi vibrator circuit, charging of capacitor occurs through resistor  $(R_A + R_B)$  and discharging through resistor  $R_B$  only. Time for charging and discharging is given as.

GATE Previous Year Solved Paper By RK Kanodia & Ashish MuroliaPublished by: NODIA and COMPANYISBN: 9788192276243Visit us at: www.nodia.co.inISBN: 9788192276243

#### **ANALOG & DIGITAL ELECTRONICS**

#### **PAGE 487**

$$T_C = 0.693 (R_A + R_B) C = 0.693 R_B C$$

But in the given circuit the diode will go in the forward bias during charging, so the capacitor will charge through resistor  $R_A$  only and discharge through  $R_B$  only.

$$\begin{array}{ll} \ddots & & R_A = R_B \\ \text{So} & & T_C = T_D \end{array} \end{array}$$

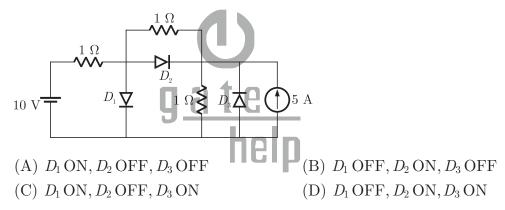

**SOL 8.47** Option (A) is correct.

First we can check for diode  $D_2$ . Let diode  $D_2$  is OFF then the circuit is

In the above circuit diode  $D_1$  must be ON, as it is connected with 10 V battery now the circuit is

Because we assumed diode  $D_2$  OFF so voltage across it  $V_{D2} \leq 0$  and it is possible only when  $D_3$  is off.

So, all assumptions are true.

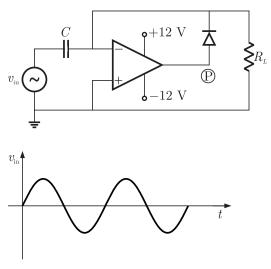

**SOL 8.48** Option (D) is correct.

In the positive half cycle of input, Diode  $D_1$  will be reverse biased and equivalent circuit is.

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |  |  |

|----------------------------------------------------------------|--|--|

| Published by: NODIA and COMPANY ISBN: 978819227624             |  |  |

| Visit us at: www.nodia.co.in                                   |  |  |

CHAP 8

Since there is no feed back to the op-amp and op-amp has a high open loop gain so it goes in saturation. Input is applied at inverting terminal so.

$$V_P = -V_{CC} = -12 \text{ V}$$

In negative half cycle of input, diode  $D_1$  is in forward bias and equivalent circuit is shown below.

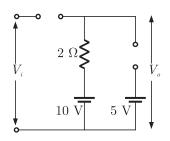

**SOL 8.49** Option (A) is correct. In the circuit when  $V_i < 10$  V, both  $D_1$  and  $D_2$  are off. So equivalent circuit is,

When  $V_i > 10$  V ( $D_1$  is in forward bias and  $D_2$  is off So the equivalent circuit is,

Output,  $V_o = V_i$ Transfer characteristic of the circuit is

**SOL 8.50** Option (B) is correct. Assume that BJT is in active region, thevenin equivalent of input circuit is obtained as

$$\begin{array}{c}

+12 \text{ V} \\

+12 \text{ V} \\

2.2 \text{ k}\Omega

\\

V_{i} \underbrace{15 \text{ k}\Omega}_{i} \underbrace{R_{th}}_{Q} \\

100 \text{ k}\Omega \underbrace{\downarrow}_{i} \\

-12 \text{ V}

\\

\underbrace{V_{th} - V_{i}}_{15} + \frac{V_{th} - (-12)}{100} = 0

\\

20 V_{th} - 20 V_{i} + 3 V_{th} + 36 = 0

\\

23 V_{th} = 20 \times 5 - 36, V_{i} = 5 \text{ V} \\

V_{th} = 2.78 \text{ V}

\\

Thevenin resistance \qquad R_{th} = 15 \text{ K}\Omega || 100 \text{ K}\Omega

\\

= 13.04 \text{ K}\Omega

\end{aligned}$$

So the circuit is

| GATE Previous Year Solved Paper By RK Kanodia & Ashish Murolia |                     |  |

|----------------------------------------------------------------|---------------------|--|

| Published by: NODIA and COMPANY                                | ISBN: 9788192276243 |  |

| Visit us at: www.nodia.co.in                                   |                     |  |

Writing KVL for input loop

$$2.78 - R_{th}I_B - 0.7 = 0$$

$I_B = 0.157 \text{ mA}$

Current in saturation is given as,

$$I_{B(\text{sat})} = \frac{I_{C(\text{sat})}}{\beta}$$

$$I_{C(\text{sat})} = \frac{12.2}{2.2} = 5.4 \text{ mA}$$

$$I_{B(\text{sat})} = \frac{5.45 \text{ mA}}{\beta} = 0.181 \text{ mA}$$

So,

$$I_{B(\text{sat})} = \frac{5.45 \text{ mA}}{30} = 0.181 \text{ n}$$

Since  $I_{B(sat)} > I_B$ , therefore assumption is true.

**SOL 8.51** Option (C) is correct. Here output of the multi vibrator is  $V_0 = \pm 12$  volt

Threshold voltage at positive terminal of op-amp can be obtained as following When output  $V_0 = +12$  V, equivalent circuit is,

writing node equation at positive terminal of op-amp

$$\frac{V_{th} - 12}{10} + \frac{V_{th} - 0}{10} = 0$$

$V_{th} = 6$  volt (Positive threshold)

So, the capacitor will charge upto 6 volt. When output  $V_0 = -12$  V, the equivalent circuit is.

node equation